必备且必会!嵌入式视觉开发减负“三件套”

demi 在 周一, 07/30/2018 - 09:57 提交

嵌入式视觉开发难不难?过来人会告诉你:难!

嵌入式视觉开发难不难?过来人会告诉你:难!

本文是该系列的第3篇,上一篇以数字滤波器的设计为主题,介绍了System Generator的完整设计流程,最后自己编写testbench在示例工程中对System Generator导出的IP核进行测试。其实System Generator就可以导出整个设计的说明文档以及一个testbench,本文将介绍如何使用该特性。

很多人拿到uboot,编译不知如何下手!

其实,这个世界上的万事万物,都有一个“纹理”。庖丁解牛之所以游刃有余,是因为他掌握了牛的纹理,顺着这些纹理就应该很容易。

那么我们的uboot的纹理在哪里呢?

在FPGA中三态门比较常见,因为FPGA是做为一个高速处理的器件,免不了要进行输入输出数据,常规的输入和输出是分开的两个接口要不停的切换比较麻烦,在FPGA中用的双向口一般都是用三态门来作为输入和输出的,这样优点是只要一个接口就可以输入输出比较节约逻辑资源,但缺点是三态门的处理没有常规两个I/O的方便,这里我们来看看怎样使用三态门,下图是三态门的结构。

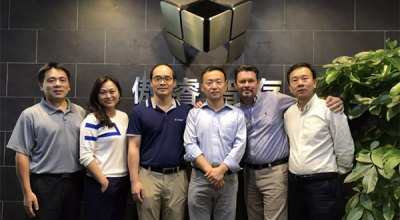

本月16至20日, Xilinx视频云战略主管Sean Gardner先生、Xilinx 中国数据中心业务拓展总监朱勇先生专程来访Aupera,并同Aupera CEO 廖玉峰博士及云服务团队一起,共同走访了中国视频云服务领域的几个领军企业,以及国内著名高校,并与相关核心研发团队、研发主管、CTO以及教授博导们开展讨论,重点就互联网视频处理及传输的未来趋势及方向,视频应用平台及云服务商如何应

AES简介

高级加密标准(AES,Advanced Encryption Standard)为最常见的对称加密算法(微信小程序加密传输就是用这个加密算法的)。对称加密算法也就是加密和解密用相同的密钥,具体的加密流程如下图:

如果你对Vivado HLS中综合之后端口的ap_none之类的类型指示摸不着头脑的话,那就来一起学习一下它们是如何使用的吧。在Vivado HLS中,我们可以指定端口使用的类型,这样在对C代码进行综合的时候,就可以指定某个端口所使用的转换协议了。常见的类型有:

1. ap_none

SDSoC、SDAccel、SDNet和HLS工具傻傻分不清楚

本文是该系列的第2篇,上一篇介绍了System Generator的基本知识以及软件的安装。本文将以一个简单的数字滤波器的设计为主题,介绍Sysgem Generator的完整设计流程,同时详细介绍使用到的各个block。

学习RCNN系列论文时, 出现了感受野(receptive field)的名词, 感受野的尺寸大小是如何计算的,在网上没有搜到特别详细的介绍, 为了加深印象,记录下自己对这一感念的理解,希望对理解基于CNN的物体检测过程有所帮助。