Optiver 使用 AMD 企业级产品组合赋能数据中心现代化,开启计算与 AI 的新时代

judy 在 周四, 05/09/2024 - 09:20 提交

Optiver 通过包括 EPYC CPU、Solarflare 以太网适配器、Virtex FPGA 和 Alveo 加速卡在内的高性能 AMD 解决方案搭建其业务基础

Optiver 通过包括 EPYC CPU、Solarflare 以太网适配器、Virtex FPGA 和 Alveo 加速卡在内的高性能 AMD 解决方案搭建其业务基础

开发板有两路千兆以太网,通过RGMII接口连接,本实验演示如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信。

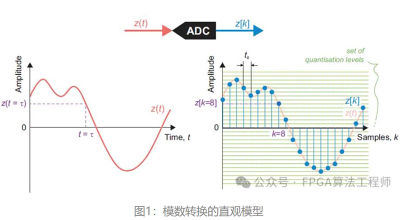

本文系摘录自《RFSoC SDR Book》第四章——DSP Fundamentals,略有改动。下面将介绍采样(Sampling)的基本概念

本篇文章将演示创建一个使用 AMD Vitis™ 视觉库的 Vitis HLS 组件的全过程。此处使用的是 Vitis Unified IDE。

当使用ram时,width是960bit,depth是16bit,只有15Kb大小, 为什么占用了很多个BRAM?

本文将会详细介绍关于DPU Fingerprint的相关内容,并提供此类校验失败问题的检查手段和解决方案。

在使用Vivado进行FPGA设计时,大家是否会遇到中文注释显示乱码的问题,而且在乱码时修改代码,导致文件注释更乱了,且恢复不了,那么如何解决呢?

2024年5月1日,PCI-SIG宣布发布 CopprLink™ 内部和外部电缆规范。CopprLink Cable 规范提供 32.0 和 64.0 GT/s 的信号传输速率

广东高云半导体科技股份有限公司与香港理工大学电气电子信息学院在港达成框架的合作意向,旨在深化双方在FPGA教育应用、电动汽车、电网传输以及智能电网等领域的合作。

AMD公布2024年第一季度营业额达55亿美元,毛利率为47%,经营收入3600万美元,净收入1.23亿美元,摊薄后每股收益为0.07美元