【视频】Xilinx 自适应计算挑战赛

judy 在 周一, 07/13/2020 - 16:07 提交

此次“自适应计算挑战赛”面向所有独立开发者和初创企业。比赛要求使用 Vitis / Vitis AI 在 Xilinx 平台上实现算法和应用的硬件加速。获奖者将获得奖金! 立即注册并开始设计吧!

此次“自适应计算挑战赛”面向所有独立开发者和初创企业。比赛要求使用 Vitis / Vitis AI 在 Xilinx 平台上实现算法和应用的硬件加速。获奖者将获得奖金! 立即注册并开始设计吧!

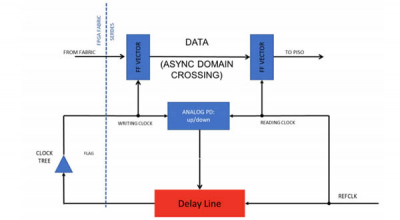

在Xilinx平台上,可实现的PTP精度受所用架构而不是硬件的限制。这是一种范式转换,它使开发人员可以在仍使用标准硬件平台的情况下达到其应用程序所寻找的精度。

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实

本篇文章参考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global。但如果认真看了Xilinx的White Paper,就会对复位有了新的认识。我们把White Paper的内容总结为下面4个问题

INT8提供了比浮点数更好的性能,精度可与AI推论相比。但是,如果INT8在有限的资源下无法满足所需的性能,则INT4优化就是答案。通过INT4优化,与当前的INT8解决方案相比,Xilinx可以在实际硬件上实现高达77%的性能提升。

现代 RF 信号链对于跨多通道的数据转换器性能具有极高的要求。换言之,对于赛灵思 RF Data Converter 而言,关键要求之一是在多个 ADC/DAC Tile、RFSoC 器件甚至开发板之间都必须保持同步。了解赛灵思如何探索多块同步 (Multi-Tile Synchronization) 问题解决之道

赛灵思与Hackster.io携手推出的首届赛灵思自适应计算挑战赛现已拉开序幕。赛灵思诚邀独立开发者和初创企业参赛,借助Vitis™ 统一软件平台和 Vitis AI 发挥杰出才能,为加速工作负载开发创意设计解决方案。两项竞赛的报名已于 2020 年 7 月 7 日正式启动。以下是本次竞赛的参赛指南

本文将着重讲述TLP的存储器、配置、IO读写请求和原子操作、消息报文几种操作请求,其中主要从其结构和特点进行分析。

恒扬数据基于FPGA的数据中心LoadBalancer加速解决方案通过提供高性能网关加速服务,可以帮助客户数倍提升基于软件的网络LoadBalance性能,快速缓解数据流量激增带来的性能压力,并大幅削减扩容带来的费用开支。

在此视频中,我们展示了一个 Xilinx 实时视频服务器一体机参考架构,该一体机使用 8 个 Alveo™U50 数据中心加速卡构建。使用此架构,在带有 AMDEPYC® 处理器的 HPE Proliant DL-385 服务器上实现高质量 1080p 实时视频流的实时解码/编码。