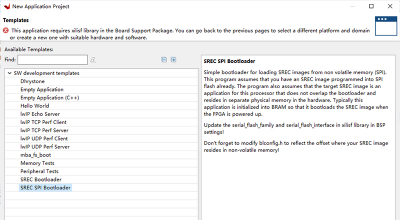

Xilinx Vitis 2020.1用SREC SPI Bootloader固化Microblaze程序,断电再通电后程序运行不了的解决办法

judy 在 周四, 11/04/2021 - 15:37 提交

FPGA的型号为XC7A35TFGG484-2,开发板用的是米联客的。主程序hello_world运行于外部DDR3内存,SREC SPI Bootloader运行于FPGA片内BRAM。

FPGA的型号为XC7A35TFGG484-2,开发板用的是米联客的。主程序hello_world运行于外部DDR3内存,SREC SPI Bootloader运行于FPGA片内BRAM。

在前面的学习中,我们已经学会了使用Vivado及SDK开发环境,熟悉了硬件开发与Linux软件驱动之间的联系及开发流程。本系列教程我们学习SDSoc的开发,在SDSoc IDE中,Xilinx为我们集成了比较流行的开发板硬件平台,如果我们使用的是其中的一个,可以直接使用。但笔者使用的是米尔科技的7z010开发板,在开发之前首先要定义我们自己的硬件平台,作为之后创建应用的模板工程

本节教程介绍如何使用SDSoC软件创建硬件平台,并且使用它来加速程序函数。

本篇文章要写的是调试Xilinx网络IP时踩到的一个坑,也是控制PHY芯片时的一个坑,板卡上的PHY芯片是非常经典的88E1111,使用MDIO接口控制。

本次设计是在zynq7035器件上进行,创建PYNQ框架v2.6版本,构建需要如下步骤:

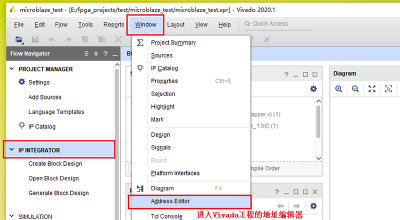

修改了代码后编译工程,有时会因为BRAM空间不足而编译失败,出现下面的错误提示,这时,需要回到Vivado工程里面,在Block Design中将分配的BRAM空间大小改大。具体方法如下。

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。

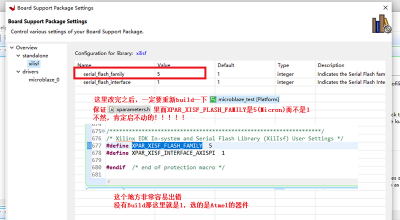

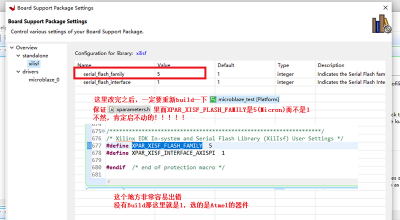

在BSP设置中,手动添加xilisf库的引用。首先,在Platform工程(这里是microblaze_test)上点击鼠标右键,选择“Open Platform Editor”命令。在Board Support Package里面,点击Modify BSP Settings按钮,勾选xilisf复选框,然后点击OK。

在前面的学习中,我们知道如何根据PetaLinux BSP设计去创建一个工程,现在,我们结合Vivado设计我们自己PetaLinux系统。

本文以XC7A35TFGG484-2这款芯片为例,采用米联客FPGA开发板,用MIG核驱动DDR3内存。FPGA外接的晶振大小为50MHz,DDR3内存的驱动频率(ddr3_ck_p和ddr3_ck_n)为400MHz。选用的DDR3内存型号为MT41K128M16,内存容量为256MB。