Xilinx FPGA DDR3设计(三)DDR3 IP核详解及读写测试

judy 在 周二, 06/06/2023 - 15:33 提交

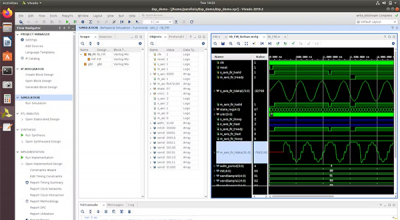

本文我们介绍下Xilinx DDR3 IP核的重要架构、IP核信号管脚定义、读写操作时序

本文我们介绍下Xilinx DDR3 IP核的重要架构、IP核信号管脚定义、读写操作时序

ROM的英文全称为Read-Only Memory,即只读存储器。可以从任意地址上读取数据

该项目介绍了如何使用 Verilog 实现具有预生成系数的简单 FIR 滤波器。

在FPGA的设计中,尤其是在通信领域,经常会遇到hash算法的实现

Vivado Schematic中的实线和虚线有什么区别?以下图为例

本文介绍如何创建Golden镜像和Multiboot镜像,以及加载失败Fallback回退的原理。

新型VPX(VITA 46)标准是自从VME引入后的25年来,对于VME总线架构的最重大也是最重要的改进

进制是人为设计的一套带进制计数方法,比如日常使用的十进制,就是0-9这10个数字

本文深入探讨在FPGA 设计中要避免的 10 大错误

本实验使用FPGA通过HDMI接口输出彩条、色带、方块等图像。