【科普】FPGA 的布局规划艺术

judy 在 周二, 08/24/2021 - 11:41 提交

布局规划是为设计增加布局布线约束的过程。一个大型高速设计的布局规划是实现时序收敛的关键。好的布局规划可以大大提高设计性能,并确保设计结果的质量。差的布局规划具有相反的效果,使其无法满足时序约束,并导致设计结果与预期不符

布局规划是为设计增加布局布线约束的过程。一个大型高速设计的布局规划是实现时序收敛的关键。好的布局规划可以大大提高设计性能,并确保设计结果的质量。差的布局规划具有相反的效果,使其无法满足时序约束,并导致设计结果与预期不符

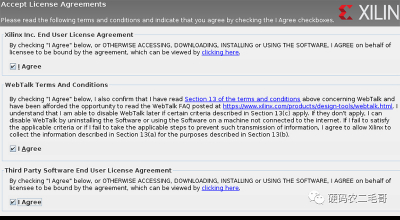

Xilinx工具最新版本已经更新到2020.2,我之所以安装2020.1主要是因为PYNQ最新版本V2.6支持2020.1,今年会做一些PYNQ相关的开发。

在文章中如何将zcu106例程移植到自定义单板,描述了如何在自定义单板平台构建硬件平台、软件系统添加配方,运行zcu106例程。实现过程很复杂。zcu106单板的bsp不能直接用在习惯单板上呢?下面是我做的一些试点,大家可以参考。

在zcu106开箱即用vcu示例中用到了USB摄像头,本节介绍如何对摄像头输出图像进行编解码。

软硬件系统构建好之后,VCU可以正常工作了。可以在VCU软件堆栈的不同层次上对VCU进行编解码,下面介绍一下使用VCU控制软件如何进行编解码。

前几节已经构建好Linux系统,但控制VCU还需要了解VCU软件架构,并加入各种库文件,也就是在Petalinxu中加入配方文件。

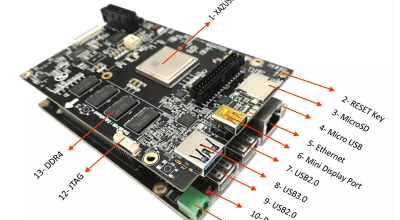

FZU5构建Linux系统过程和FZU3类似,FZU3构建过程参照前一篇文章。下面主要描述一下不同的地方。

硬件设计主要包括PS设置和VCU设置,VCU参考了pg252和zcu106例程,如下图所示。FZU5输入25MHz时钟,通过PLL产生33MHz和300MHz时钟输入到VCU。此外,PL部分还需要产生风扇控制信号,控制单板风扇。

yolo是目前目标检测落地到硬件中比较常用的AI模型,因为yolo标准版模型参数和计算量太大,所以目前暂时在zynq020上移植的是tiny版本,这里选用yolov3-tiny来移植,输入模型的图像源320x320@15Hz,模型各层如下(其中C是训练时的类别)

本次设计目标是将ZCU106使用的例程移植到自定义单板上。例程指的是pg252中开箱即用7个例子。