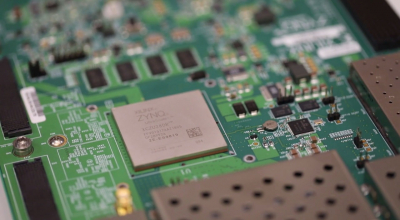

基于ZYNQ MPSOC XCZU3CG的百度Edgeboard FZU3 构建linux系统

judy 在 周四, 08/05/2021 - 10:09 提交

本文在上篇基础上描述在FZU3上运行DPU例程的方法。

本文在上篇基础上描述在FZU3上运行DPU例程的方法。

百度Edgeboard FZU3硬件平台构建和软件系统构建

近期在研究FPGA进行推理时,总结了一下三种方案,目前我了解使用FPGA进行推理还是少数,不知道大家有没有做过使用FPGA进行推理的项目,欢迎交流。

“重构”对于刚接触FPGA的人来说,可谓十分神秘,对于已经入门的人来说很“简单”,但是你真的了解FPGA的重构吗?

Vivado ML 版支持基于机器学习的算法以加速设计收敛。该技术具备基于机器学习的逻辑优化、延迟估算和智能设计运行,能够自动执行策略以减少时序收敛迭代,将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量提升

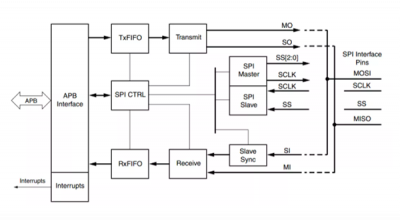

SPI 总线控制器支持与各种外设通信,例如存储器、温度传感器、压力传感器、模拟转换器、实时时钟、显示器和任何支持串行模式的SD卡等等。SPI 控制器可以在主模式、从模式或多主模式下工作。Zynq-7000 器件包括两个 SPI 控制器,该控制器基于 Cadence SPI 内核。

ZYNQ中的AXI接口包含三个类型,共9个,主要用于PS与PL的互联。今天我们重点来说一下ACP接口。

TTC 包含三个独立的定时器/计数器,PS中有两个TTC模块,总共有六个定时器/计数器,TTC 1 控制器可以配置为安全或非安全模式,使用nic301_addr_region_ctrl_registers.security_apb [ttc1_apb] 寄存器位。TTC 控制器内的三个定时器具有相同的安全状态。

利用SDR做一个收音机是所有入门SDR都会做的小项目,简单直观易上手的特点和“Hello World”、流水灯一样。本篇文章就带领大家利用AD936X+ZYNQ平台SDR做个SDR。

对于GP接口(general purpose)通用目的接口,有四个接口(两个从端口,两个主端口)。GP接口直接连接到的是中央互联区(central interconnect),然后由中央互联区再连接到OCM interconnect和存储器接口上。对于GP接口,通常使用他进行控制配置。