存储器相关问题汇总【SRAM】【DRAM】【SDRAM】【Flash】【EPROM】【EEPROM】

judy 在 周五, 05/14/2021 - 09:25 提交

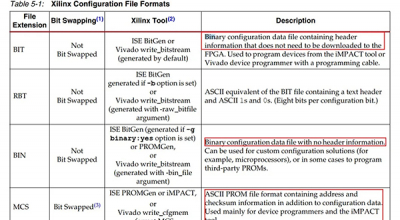

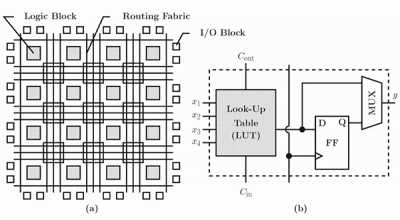

很多 FPGA 也是基于 SRAM 架构的,下载程序后运行,而断电后再次上电,需要重新下载程序。由此引出所谓的“固化”,即将程序下载到 EEPROM、Flash 等非易失性器件中,每次上电后从 EEPROM 或者 Flash 中加载对 FPGA 的配置(bitstream),比如 Xilinx FPGA 常用 QSPI Flash、SD 卡等方式。