ZYNQ自定义AXI总线IP应用——PWM实现呼吸灯效果

judy 在 周四, 03/19/2020 - 09:23 提交

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

基于JESD204数字接口的数据转换器正在兴起,目前渐渐取代了部分基于LVDS接口的数据转换器,这种趋势就如同十几年前基于LVDS接口的数据转换器开始取代基于CMOS接口的数据转换器情形一样。

Vitis 被 Xilinx 称为 “统一软件平台”,从目前已了解的情况来看,嵌入式软件开发在 Vitis 上更为简单方便。从 ISE 到 Vivado,再到 Vitis 的升级趋势来看,Vitis 将是未来数年的开发主力。

在前面的文章中ZCU106 XRT环境搭建【Xilinx Vitis】,已经生成了用于在Vitis的相关环境。Xilinx在GitHub分享了一个Vitis的应用程序加速开发的教程:2019.2 Vitis™ Application Acceleration Development Flow Tutorials

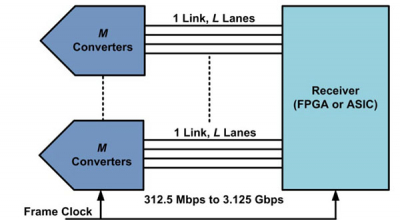

2006年4月,JESD204标准的最原始版本诞生,该标准描述了数据转换器(ADC或DAC)和接收器(FPGA或者ASIC)之间的吉比特串行数据传输链路(link)。在这个原始标准中,一个或多个数据转换器与接收器之间的串行链路被定义为有且只有一条数据通道(lane)

在ZCU106 XRT环境搭建【Xilinx Vitis】中针对我本地的环境,以及ZCU106的需求,生成了最终使用的PetaLinux工程。PetaLinux工程的创建、编译都是使用脚本peta_build.sh 来完成的。这篇文章分析一下我本地的不同于ZCU102、ZCU104的区别。

Xlinx的ZYNQ系列SOC集成了APU、各种专用外设资源和传统的FPGA逻辑,为ARM+FPGA的应用提供助力,降低功耗和硬件设计难度的同时极大提高两者间传输的带宽。之前在研究生课题中使用过ZYNQ搭建环路系统对算法进行板级验证

在上一篇ZCU106 XRT环境搭建【Xilinx Vitis】中,我参考了XRT中其它平台(ZCU102,ZCU104)的Vivado TCL脚本,同时参考了官方的VCU相关工程,编写了ZCU106 XRT的脚本。在这篇文章中将对该工程进行一下分析。

最近在看Xilinx新出的工具Vitis,这个工具咋说呢,改了好多。。

之前的SDSoC,SDAccel统一被Vitis来实现

之前按的SDK直接被Vitis替代

IO管脚约束是FPGA设计上板验证的必需环节,它们会对布局布线和时序造成影响。有三种方式来进行管脚约束,一种是通过VIvado管脚约束界面,一种是通过命令行,还有一种可以导入CSV文件