Verilog的未来在哪里?

judy 在 周一, 03/31/2025 - 10:18 提交

在FPGA的群里,经常会有人讨论以后Verilog会如何发展?HLS和DLS谁会胜出?用Python来写更快还是现在用的相对多一些的Chisel和SpinalHDL?

在FPGA的群里,经常会有人讨论以后Verilog会如何发展?HLS和DLS谁会胜出?用Python来写更快还是现在用的相对多一些的Chisel和SpinalHDL?

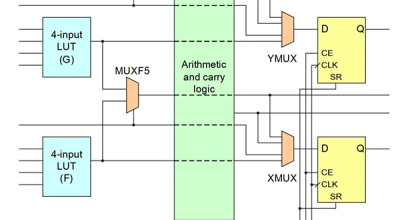

今天主要对Xilinx、Altera和Actel三家 FPGA 中使用的逻辑单元架构进行对比,最后对这三家逻辑量换算进行说明

在无线充电、物联网和汽车电子等领域,ASK解调技术正悄然成为高效通信的“幕后功臣”。本文将带你深入探索这一技术的核心原理、创新突破与未来潜力。

近年来,国产 FPGA 发展迅速,中国共有22家(去除特殊用途的反熔丝还有19家)FPGA厂商,主要有紫光同创、安路科技、复旦微等。

今天给大侠带来的是一周掌握FPGA Verilog HDL 语法,今天开启第一天,下面咱们废话就不多说了,一起来看看吧。

在实际应用中,数据转换过程会产生噪声和杂散,它们会扭曲和干扰原始信号,影响系统的整体性能。

该系列教程由 AMD 的工业架构师 Tomas Thoresen 在 Hackster 上利用 FPGA 进行机器人应用的探索,下面先介绍一下这个项目

图像处理中最常用的技术之一是使用滑动窗口滤波器,该滤波器在图像上滑动一个 nxn 矩阵并对中心像素进行操作。

前面两篇文章详细介绍了DFT和FFT,今天介绍一下使用Verilog实现8点FFT。

本文介绍emacs中调用verible lint来检查verilog语法方法。