Xilinx AXI VIP使用教程

judy 在 周四, 07/27/2023 - 09:39 提交

本次内容我们看下AXI VIP当作master时如何使用

本次内容我们看下AXI VIP当作master时如何使用

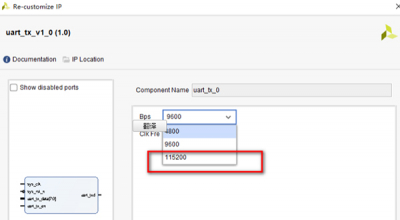

UART即通用异步收发器,是一种通用串行数据总线,用于异步通信

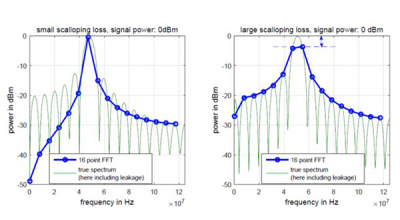

本文主要解释如何用FFT精确地测量信号功率(signal power)

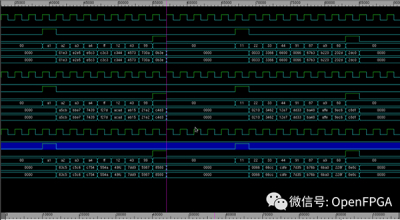

项目在上板测试过程中必现报文被丢弃的现象,方案不是很复杂

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核

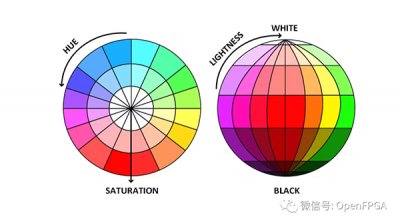

颜色空间转换是图像及视频中常用的解决方案

本文将向大家介绍Xilinx FPGA下的MIG IP核使用方法

作为一个开发者,我们都有过将写好的,或者修改后的代码上传服务器的经历

在使用xilinx官方例程《XAPP585》实现CameraLink接口发送或者接收数据时,有个程序还是值得学习的

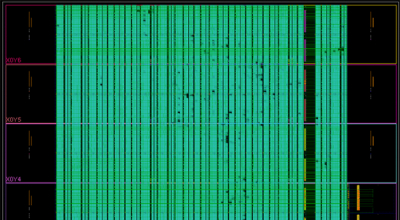

FPGA综合与布线效率研究