使用Petalinux的boot文件、根文件系统,和开源Linux的Image启动

judy 在 周一, 03/07/2022 - 10:17 提交

Petalinux编译后,在images/linux里,既有Image,也有image.ub。image.ub已经带文件系统,可以独立启动。

Petalinux编译后,在images/linux里,既有Image,也有image.ub。image.ub已经带文件系统,可以独立启动。

在zynq7035单板创建PYNQ镜像V2.6中介绍了,如何在zynq7035单板上创建PYNQ。在开发的过程也是一次次迭代的过程,如果遇到问题,需要重新构建硬件和PYNQ,下面就介绍一下,修改硬件平台后,PYNQ的开发流程。

primary clocks是vivado时序分析工具认为的时钟源点,一定要定义在最初始端。primary clocks只能用create_clk命令来定义。

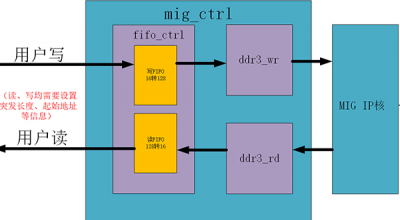

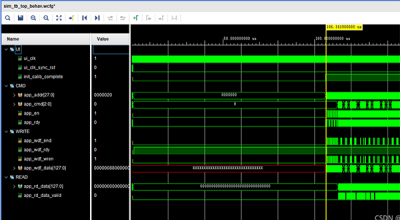

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

本部分通过将 HLS IP 和 Testbench 设计发送给编译器进行编译和执行,来执行 HLS 流的 C仿真阶段。

使用DSP的方法一般有两种:让综合器自己推断、例化DSP原语。有的时候为了偷懒或者有的计数器之类的需要跑高速,则可以让计数器也使用DSP实现。

在我心中,Xilinx是一家完美的公司,技术生态支持实在是做的太好了。Xilinx也知道我们不会用DDR3,所以提供了一个example design给你学习,怎么样?惊不惊喜?意不意外?

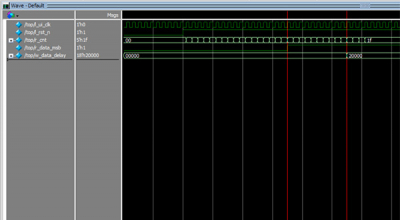

对于xilinx移位寄存器IP的使用而言,其内部为SLR16/SRL32实现。当位深小于32时,其可变延迟是正确的。当大于32,其可变延迟为相同延迟加1。

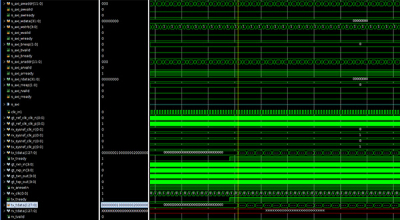

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合