【FPGA技巧篇】时钟设计技巧

judy 在 周一, 02/21/2022 - 10:15 提交

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。

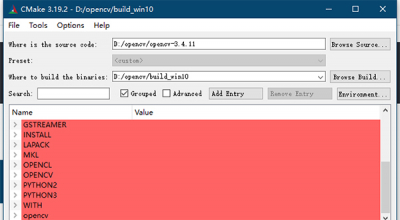

Vitis HLS OpenCV库编译

如图所示, 源文件目录中haha文件夹下有一个hoho.h头文件。本来要包含这个头文件应该写成#include "haha/hoho.h"的,但是如果写成#include

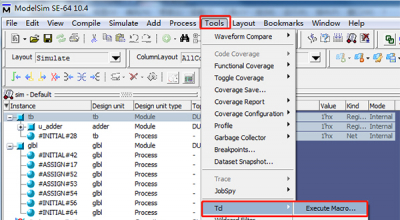

老鸟的姿势学起来,用脚本进行modelsim仿真

先从运行一个创建一个项目开始吧。

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错

同步电路系统设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是FPGA设计的基础。但是伴随着集成电路的微缩化和大规模化,同步式电路的一些问题也显现出来。

在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个?

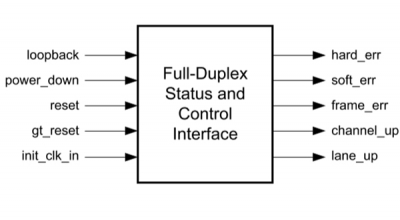

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?黑盒子就是你看不到里面的东西,你只能看到外面的接口。