机器学习三个时代的计算趋势

judy 在 周三, 04/13/2022 - 16:53 提交

基于这些观察,机器学习的计算历史被划分为三个时代——前深度学习时代、深度学习时代和大规模时代。本文总结了用于训练高级机器学习系统快速增长的计算需求。

基于这些观察,机器学习的计算历史被划分为三个时代——前深度学习时代、深度学习时代和大规模时代。本文总结了用于训练高级机器学习系统快速增长的计算需求。

本人业余搞FPGA开发的同时,还喜欢研究生产力工具,包括硬件和软件的,电脑就是重中之重,恰好今年手中有个还算比较大FPGA工程,综合一次相当费时,索性把以前记录的

本文对VDMA模块功能、性能、寄存器和软件编程方法进行简要介绍。

上一篇文章我们讲到7系列FPGA的时钟结构,这篇文章我们来看下clock region内部都有哪些东西?

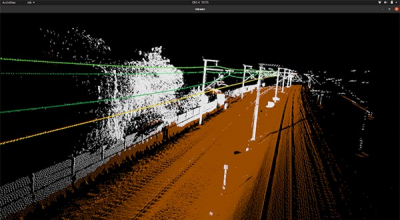

现在有许多其他的传感器技术,可以完善或增强传统相机的功能。在本文中,我们将讨论其中三个常见的机器视觉技术。

本文介绍如何自己编写AXI4-Stream slave类型的图像源。

从本篇文章开始,我们来介绍下Xilinx FPGA的时钟结构、资源、用法,首先从7系列的FPGA开始,因为7系列的FPGA结构跟前面的有很大不同,而且前面那些FPGA用的也越来越少了。

本文通参考MATLAB的RF仿真工具,展示如何在发射机中使用数字预失真(DPD)来抵消功率放大器中非线性的影响。

本文写了三个示例,展示了三种综合脚本的写法,供大家可以参考。

本文介绍MATLAB的混频测试