基于FPGA的数字信号处理(6)--定点数据的两种溢出处理模式:饱和(Saturate)和绕回(Wrap)

judy 在 周五, 09/20/2024 - 15:36 提交

本文只讨论整数部分的溢出截位处理,小数部分的处理下篇文章再说。对整数的截位处理,实际上就是对溢出的处理

本文只讨论整数部分的溢出截位处理,小数部分的处理下篇文章再说。对整数的截位处理,实际上就是对溢出的处理

该层具有接收ARP请求、发送ARP回复,和发送ARP请求、接收ARP回复的功能,并将接收到的对端的地址信息存入cache中

为了使运算结果不错误溢出从而导致功能错误,我们应该对运算结果的位宽进行合理的扩展,使其在不浪费资源的情况下保证运算结果的正确性

ICMP层数据和UDP层数据都要经过IP层打包或者解包,IP层主要功能为判断数据报文类型,进行IP首部校验,添加包头或者过滤包头,处理ICMP请求。

很多时候,Verilog中表达式的位宽都是被隐式确定的,即使你自己设计了位宽,它也是根据规则先确定位宽后,再扩展到你的设计位宽

今天,我们一起来探讨三态门的基本原理、在Verilog中的实现方式。

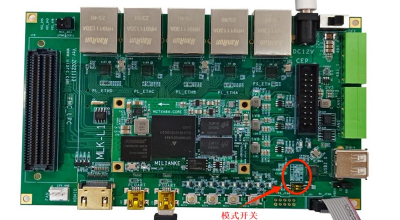

我们在正常升级的过程(只使用一个位流文件),假如:(1)因为干扰通信模块收到了一个错误位;(2)或者烧写进FLASH时突然断电

由于IP和ARP数据包送至MAC层要经过同一个通道,需要对发送的数据包类型进行判断和仲裁,这就需要额外增加一个IP_ARP层

尽管signed语法的使用能带来很多便利,但同时也给表达式的符号确定带来了更多的不确定性。比如一个有符号数和一个无符号数的加法/乘法结果是有符号数还是无符号数?