Xilinx Vitis学习教程:ZYNQ之lwip使用Echo server(3)

judy 在 周五, 04/03/2020 - 09:44 提交

疫情期间是真爽,睡觉睡得我啥也不想干,本来也琢磨着继续更新,无奈开工就很忙,天天只想睡觉,自从爽了一个月,我就只想睡觉,看来我要买点亚麻籽油提提神了,碰巧最近有网友问他的双核没法正常工作,我试了下,是可以的,但是这当中也遇到点bug,好吧,开始干活吧

疫情期间是真爽,睡觉睡得我啥也不想干,本来也琢磨着继续更新,无奈开工就很忙,天天只想睡觉,自从爽了一个月,我就只想睡觉,看来我要买点亚麻籽油提提神了,碰巧最近有网友问他的双核没法正常工作,我试了下,是可以的,但是这当中也遇到点bug,好吧,开始干活吧

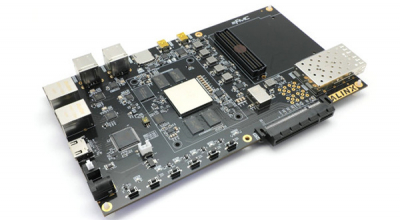

Ultra96板子是AVNET开发的,看价格也是比较便宜的。是基于Xilinx Zynq UltraScale+ MPSOC系列的芯片,具体使用的是:Xilinx Zynq UltraScale+ MPSoC ZU3EG SBVA484。板子本身比较比较小,外设模块也很少,其主要特点及开发板框架如下所示

Xilinx公司的JESD204 IP核能够实现复杂的JESD204B协议,支持的速度范围为1Gbps~12.5Gbps。该IP核可以被配置成发送器或者接收器,不能配置成同时收发。目前该IP核仅支持vivado软件,不支持ISE,且仅支持xilinx公司的7系列及其以上系列的FPGA硬件。该IP核的主要特性包括以下几点

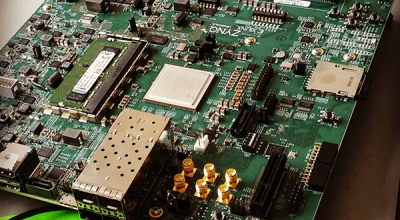

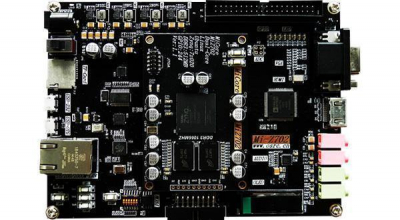

继续学习ZYNQ,吃了好几年灰的ZYNQ 7020开发板一直没时间玩,现在稍微有点时间,准备空闲之余折腾一下,之前一直使用STM32等各式单片机,LINUX知识也知道一点,对HDL也是一窍不通,现在准备恶补一下,对于我来说,学习固然重要,但是白费力折腾也是要有的

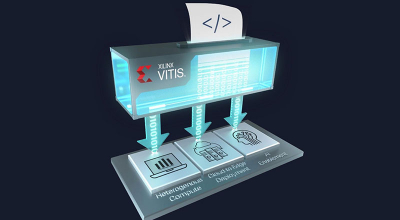

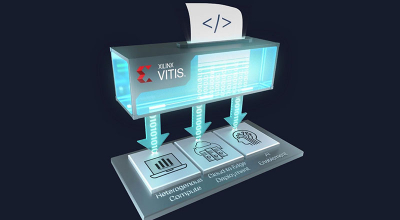

或许是每个做硬件的厂商都有做软件的心,xilinx发布了他的下一个平台Vitis,也就是硬件和软件分开了(即Vivado和IDE分开了),除了启动方式和使用方法略有区别外,其他操作几乎与上一代Vivado一模一样。本文是试用这个新平台来尝尝鲜。

具体方法与 SDK 的多核工作实现方法基本一致,详细操作可以参考 zcu102 系列文档。本文的代码工程继承 vitis_zcu102_1 文档。

这次主要分享一下Xilinx官方的QTV:如何在 Alveo 卡上快速使用 Vitis 进行开发的视频,主要是可以对Vitis有个快速的认识。

APU系统中CPU以串行执行代码的方式完成操作,软件方式很难做到精准计时,因此调用内部定时器硬件完成计时是更好的选择。本文以定时器中断方式控制LED周期性闪烁为例学习私有定时器的使用。同时学习如何将软件程序与硬件比特流文件一起固化到SD卡中,实现上电自动配置与启动自定义系统

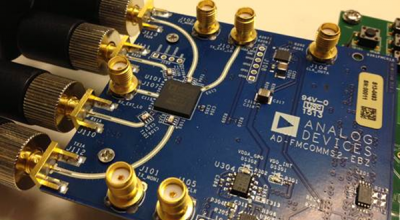

JESD204B是JEDEC委员会制定的一种串行接口标准,这种接口标准定义了数据转换器(ADC、DAC)和数字处理器(FPGA、 ASIC等)之间的数字信号传输方式。它作为第三代标准,补充了JESD204、JESD204A这前两代标准的不足之处。

上一篇安装完相关程序后,这一篇就简单运行一个“Hello Vitis”的程序。本例硬件平台为ZYNQ平台,具体芯片为XC7Z035。ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,而且不需要在 Vivado 软件里分配管脚,虽然本实验仅仅使用了 PS,但是还要建立一个 Vivado 工程,用来配置 PS 管脚