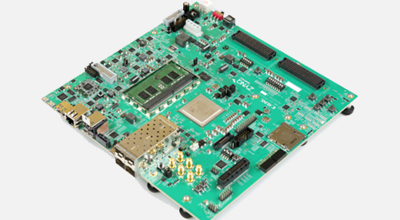

ZCU102(5)——AXI_BRAM实现PL与PS数据互联

judy 在 周五, 08/23/2019 - 08:41 提交

PS模块通过axi_bram模块,可以使用AXI接口读写PL内的Block RAM,实现PS与PL之间的数据互联。axi_bram需要与Block Memory Generator模块共同使用,axi_bram将PS的AXI操作转化为bram的控制接口时序。建立Vivado工程,并且添加Zynq模块,AXI BRAM Controller模块,Block Memory Generator模块,Utility Vector Logic模块和ILA模块。