ZCU106 XRT PetaLinux工程分析【Xilinx Vitis】

judy 在 周五, 03/13/2020 - 10:43 提交

在ZCU106 XRT环境搭建【Xilinx Vitis】中针对我本地的环境,以及ZCU106的需求,生成了最终使用的PetaLinux工程。PetaLinux工程的创建、编译都是使用脚本peta_build.sh 来完成的。这篇文章分析一下我本地的不同于ZCU102、ZCU104的区别。

在ZCU106 XRT环境搭建【Xilinx Vitis】中针对我本地的环境,以及ZCU106的需求,生成了最终使用的PetaLinux工程。PetaLinux工程的创建、编译都是使用脚本peta_build.sh 来完成的。这篇文章分析一下我本地的不同于ZCU102、ZCU104的区别。

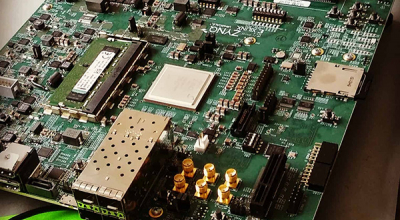

Xlinx的ZYNQ系列SOC集成了APU、各种专用外设资源和传统的FPGA逻辑,为ARM+FPGA的应用提供助力,降低功耗和硬件设计难度的同时极大提高两者间传输的带宽。之前在研究生课题中使用过ZYNQ搭建环路系统对算法进行板级验证

在上一篇ZCU106 XRT环境搭建【Xilinx Vitis】中,我参考了XRT中其它平台(ZCU102,ZCU104)的Vivado TCL脚本,同时参考了官方的VCU相关工程,编写了ZCU106 XRT的脚本。在这篇文章中将对该工程进行一下分析。

最近在看Xilinx新出的工具Vitis,这个工具咋说呢,改了好多。。

之前的SDSoC,SDAccel统一被Vitis来实现

之前按的SDK直接被Vitis替代

IO管脚约束是FPGA设计上板验证的必需环节,它们会对布局布线和时序造成影响。有三种方式来进行管脚约束,一种是通过VIvado管脚约束界面,一种是通过命令行,还有一种可以导入CSV文件

axi_timer模块即为PS可以访问的PL计数器,通过计数值以及接入axi_timer的计数时钟周期,可以在PS内取得比较精确的计时。axi_timer有2种使用方式,一种是作为计数器使用,另一种是作为定时器使用

在业界,串口又称为通用异步收发器(Universal Asynchronous Receiver/Transmitter,简称UART),它的通信方式遵循一套串口协议:UART通信首先将接收到的并行数据换成串行数据来传输。数据帧从起始位开始,后面是7个或8个数据位,一个可用的奇偶校验位和一个或几个高位停止位

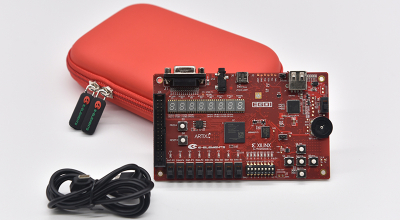

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

前面我们已经学习了TCP的所有发送、接收和各种回调函数。本文将介绍最后一部分,TCP的轮询机制。在前面TCP发送Hello World的实例中,我们是在main函数的while循环中每隔1s调用一次数据发送函数。本文的实例将利用轮询机制完成同样的功能。

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1。打开Vivado,创建一个名为design_test的空白工程。点击Add source或者Sources中的+号来添加或者创建一个设计源文件,点击Next。