Vitis_ZCU102_2_Vitis 实现 Bare-Metal 工程

judy 在 周一, 03/23/2020 - 09:34 提交

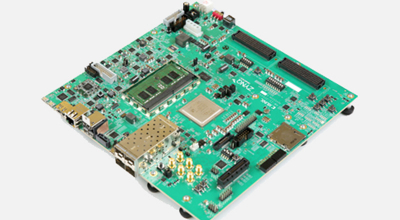

建立基于 zcu102 开发板的 Vivado 工程。建立 Block Design,添加 Zynq UltraScale+ MPSoc 的 IP。点击 Run Block Automation,自动配置 IP 模块。双击打开配置窗口查看 UART 0 和 UART 1 已按照 zcu102 开发板的硬件连接设置完成。

建立基于 zcu102 开发板的 Vivado 工程。建立 Block Design,添加 Zynq UltraScale+ MPSoc 的 IP。点击 Run Block Automation,自动配置 IP 模块。双击打开配置窗口查看 UART 0 和 UART 1 已按照 zcu102 开发板的硬件连接设置完成。

vitis虽然已经发布很长时间了,但是我就要尝鲜。。。首先是安装,本教程分两个主要的平台(WIN10和Ubuntu)给出安装教程和源文件。

ADC芯片会包含许多性能参数,而我们在选择ADC芯片时,其中有一项关键性的参数值得关注,即数字化的数据输出接口类型(the type of digital data output)。目前在高速ADC芯片中,使用最广泛的数据输出接口类型有3种

本篇文章来测试Tutorials中的第2个例子:Mixing C++ and RTL Kernels。该例子中进行了两个步骤的实验,分别是sw_emu和hw_emu,我这变还是会继续在硬件上直接测试。

作者:bt_

原文链接: https://blog.csdn.net/botao_li/article/details/103901856

* 本文由作者授权转发,如需转载请联系作者本人

主要参考:ug1400

安装串口调试软件

安装串口软件 tinyserial

本人使用 Qt 5.12.6 编译后使用(deb 安装后无法运行)。

建立 Platform Project

在实时性要求较高的场合中,CPU软件执行的方式显然不能满足需求,这时需要硬件逻辑实现部分功能。要想使自定义IP核被CPU访问,就必须带有总线接口。ZYNQ采用AXI BUS实现PS和PL之间的数据交互。本文以PWM为例设计了自定义AXI总线IP,来演示如何灵活运用ARM+FPGA的架构

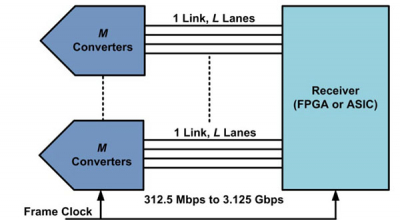

基于JESD204数字接口的数据转换器正在兴起,目前渐渐取代了部分基于LVDS接口的数据转换器,这种趋势就如同十几年前基于LVDS接口的数据转换器开始取代基于CMOS接口的数据转换器情形一样。

Vitis 被 Xilinx 称为 “统一软件平台”,从目前已了解的情况来看,嵌入式软件开发在 Vitis 上更为简单方便。从 ISE 到 Vivado,再到 Vitis 的升级趋势来看,Vitis 将是未来数年的开发主力。

在前面的文章中ZCU106 XRT环境搭建【Xilinx Vitis】,已经生成了用于在Vitis的相关环境。Xilinx在GitHub分享了一个Vitis的应用程序加速开发的教程:2019.2 Vitis™ Application Acceleration Development Flow Tutorials

2006年4月,JESD204标准的最原始版本诞生,该标准描述了数据转换器(ADC或DAC)和接收器(FPGA或者ASIC)之间的吉比特串行数据传输链路(link)。在这个原始标准中,一个或多个数据转换器与接收器之间的串行链路被定义为有且只有一条数据通道(lane)