FPGA实现LVDS接口(1)--IBUFDS原语、OBUFDS原语和IOBUFDS原语的介绍及使用

judy 在 周五, 01/10/2025 - 09:54 提交

IBUFDS原语、OBUFDS原语以及IOBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换

IBUFDS原语、OBUFDS原语以及IOBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换

实现时序收敛的关键要素之一是确保我们编写出能够充分利用设备架构特性和实现工具功能的优质代码。让我们来看看可以帮助我们提供更好质量代码的几个方面。

今天要分享的是一个简单的MIPI到LVDS(DVP)接口转换的案例。目的就是要把低成本FPGA的应用潜力充分利用起来。

很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法

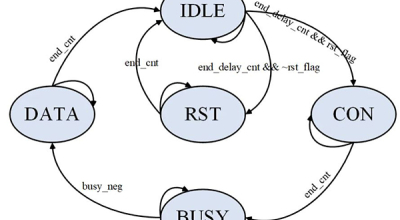

前文讲解了AD7606的功能及原理,本文通过FPGA实现AD7606的并行接口数据采集,对应时序如下所示

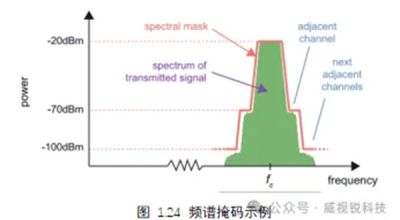

脉冲包含所有频率,通过无线电信道传输脉冲将产生带宽极宽的无线电信号,这些信号会侵入相邻频带,对其他用户造成干扰。

WM8731是集成耳机驱动器的低功耗立体声编解码器,有2路24位的ADC及DAC,支持16~32位的数字音频输入字长和8kHz~96kHz的采样速率

本文介绍PCIe IP核时钟结构、PCIe板卡时钟方案及复位设计相关内容。

本文将详细介绍图像镜像算法的基本原理、Python实现以及FPGA实现。

在 FPGA 上实现延时定时(Delay Timing)通常需要根据实际需求选择高效的方法,以下是两种常见且高效的实现方法