当前挑战:在以太网中实现精确时序

传统以太网在通用网络领域表现可靠,但在自动化技术领域,却难以满足其不断演进的需求。自动化技术应用对网络有诸多严格要求,例如需要实时控制、微秒级的时间同步、稳定的带宽保障以及超低的时延调度。面对这些需求,各类专有总线系统应运而生。

这些专有总线系统虽然在物理层采用以太网,但各自采用不同的实时协议,导致了供应商依赖和网络碎片化的问题。且这些系统往往通过隔离时间关键型数据流量与次要流量来避免干扰,然而在未来工业 4.0 应用、汽车系统或航空电子等前沿领域,对以太网的一致性和集成度有更严苛的要求,这种隔离方式已无法满足需求。

时间敏感网络 (TSN) 正是基于成熟完善的标准以太网技术发展而来的一套协议体系,旨在更好地满足这些需求。TSN 可提供标准化解决方案,确保在以太网上实现可靠、具确定性且低时延的通信。它能够实现关键与非关键数据流量在单一网络上的融合,无需独立的基础设施,从而有效降低成本。通过确保低时延并消除供应商依赖,TSN 已成为实时通信的关键技术。

不过,高效整合这些复杂的 TSN 机制已经超越了普通网络接口的能力范围,因此需要采用专用的软硬件。作为芯片 IP 和通信协议领域的专家,CAST 与 Fraunhofer IPMS 走在行业前列,基于 Altera FPGA 的解决方案实现了更出色的灵活性和更优异的资源效率。

基于 Altera FPGA 的紧凑型 TSN IP

CAST 与 Fraunhofer IPMS 提供 TSN 端点、TSN 交换机和 TSN 交换端点 IP 核,可用于构建旨在突破标准以太网局限性的 TSN 以太网网络。相较于低集成度方案,该解决方案通过将关键时间同步和流量调度功能直接嵌入硬件,为确定性通信提供了重要基石。这些 IP 核针对资源效率进行了优化,可显著减少 FPGA 内部逻辑需求,实现更加经济高效的设计,同时可灵活定制 TSN 节点以满足特定应用需求。

Altera FPGA 可提供大多数 TSN 应用所需的灵活性和效率。TSN 通常是工业自动化或车载网络的重要支柱,其节点往往通过 SPI、CAN、PWM 等多种接口与传感器或执行器通信,并可能需要运行复杂程度各异的软件层。通过在 Altera FPGA 上部署 TSN,开发人员能够在同一高性价比设备上实现不同接口、设备驱动及软件应用层。

Altera FPGA(如低功耗且经济高效的 Cyclone® V SoC FPGA)凭借其出色的灵活性和性能以及丰富的 IP 生态系统,提供了更理想的硬件基础。TSN IP 采用数字化紧凑设计,可轻松移植至全新 Altera 设备家族,包括高性能、高能效的 Agilex™ 3 FPGA,或集成 AI 模块的中端 Agilex™ 5 FPGA。

经验证的 TSN IP 核

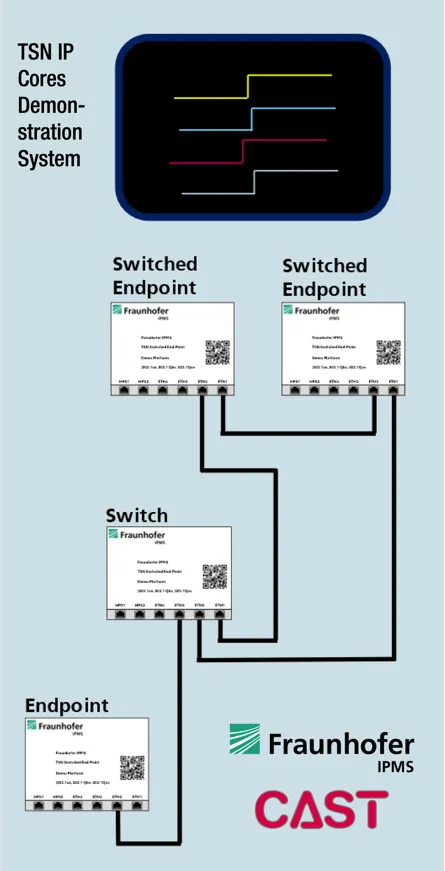

CAST 提供三种可在 Altera 设备上实现的 TSN IP 核:

多端口 TSN 以太网交换机,支持直通式、超低时延运行 ;

TSN 以太网端点,适用于星型网络拓扑结构 ;

TSN 以太网交换端点,适用于菊花链网络 。

这些 TSN IP 核均由 Fraunhofer IPMS 开发,严格遵循 CAST 的高标准 IP 质量要求,提供更加高效、易于集成且低风险的硬件实施方案。这些 IP 核支持关键 TSN 时间同步及流量整形协议,如 IEEE 802.1AS-2020、802.1Qav、802.1Qbv、802.1Qbu 和 802.1br,并可选择附加 TSN 协议,以实现更高的可靠性以及针对特定应用的操作。且具备可配置功能及可选 DMA 引擎等属性,使其成为更加多样化且更高效的 TSN 解决方案。

成果展示:显著优化网络时间同步

CAST 与 Fraunhofer IPMS 共同展示了其 TSN IP 解决方案在 Altera Cyclone® V SoC FPGA 设备上的高效表现。

该演示系统连接了四块 Altera 板卡,分别配置为 TSN 交换机、两个交换端点及一个端点。通过示波器观察到,每块板卡每隔数秒就会生成一个信号,成功验证了该解决方案的全网时间同步能力。

即便人为断开一条网线破坏环形拓扑,内置冗余功能仍能使其余网络节点保持精确同步。唯有当第二根网线被移除导致设备完全隔离时,其信号才会出现漂移和失步,这表明了 TSN 同步机制在整个互连网络中的有效性。

立即体验全新解决方案

在工业、汽车或航空电子等对技术精度要求严苛的应用中部署 TSN 网络时,稳定、高效、可靠缺一不可。而 Altera 的 FPGA 产品线,从历经市场验证的 Cyclone® V SoC FPGA ,到性能跃升、更多样化的 Agilex™ 3 和 Agilex™ 5 家族,正为这类场景构建了坚实的硬件底座。

若您正致力于在这些严苛领域推进 TSN 技术落地,可通过 CAST 获取由 Fraunhofer IPMS 研发的经实践验证的紧凑型 IP 核。硬件平台的强劲性能与成熟 IP 核的有机结合,不仅为 TSN 部署提供了双重保障,更能有效简化复杂流程,让技术落地之路更为顺畅。

文章来源:Altera FPGA