AMD 7nm Versal系列器件引入了可编程片上网络(NoC, Network on Chip),这是一个硬化的、高带宽、低延迟互连结构,旨在实现可编程逻辑(PL)、处理系统(PS)、AI引擎(AIE)、DDR控制器(DDRMC)、CPM(PCIe/CXL)等模块之间的高效数据交换。

NoC的出现,替代了传统PL内部布线实现复杂总线互连的方式,通过专用硬化通道提升吞吐量、降低延迟、减少逻辑资源占用,并且能实现跨Die(SSIT封装)的高速通信。

NoC架构与特性

NoC包含以下主要组件:

NMU(NoC Master Unit):将AXI请求转换为NoC数据包(NPP),支持时钟域转换与速率匹配;

NSU(NoC Slave Unit):接收并解析NoC数据包(NPP),转换为AXI协议;

NPS(NoC Packet Switch):全双工交换机,连接多个NoC节点;

NIDB(NoC Inter-Die Bridge):跨Die的垂直NoC桥接模块。

核心特性

水平(HNoC)与垂直(VNoC)通道:减少PL内布线压力,提高拓展能力;

AXI接口灵活配置:支持32位~512位AXI Mem位宽,以及128位~512位AXI4-Stream;

自动交错访问:跨多个DDR控制器分配请求,提升带宽利用率;

QoS(服务质量):提供基于延迟/带宽的优先级控制;

跨Die通信:多Die设计中提供高效数据通道;

硬化路径固定延迟:相比可编程互连,延迟更可预测,利于实时应用。

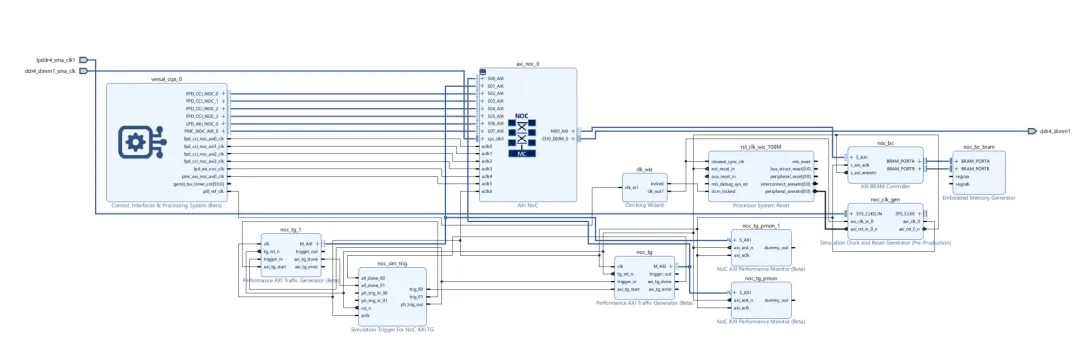

此文结合Vivado工程,快速熟悉NoC的使用

Vivado中的NoC使用步骤:

1. 新建工程 & BD→添加Versal NoC IP

2. 配置AXI\_Slave(NMU)与AXI\_Master(NSU)

3. 连接DDR控制器、CPM、AI Engine等模块

4. 在NoC Compiler中查看拓扑,配置QoS、带宽、路由路径

5. 必要时在XDC中固定NMU/NSU位置以减少路径延迟

6. 分析带宽与延迟,迭代优化

NoC内部的组件

1、NoC Master Unit (NMU)

NMU的作用是将AXI协议转换为NoC数据包协议(NPP),同时,NMU还支持AXI端口和NoC之间的异步时钟域转换与速率匹配。

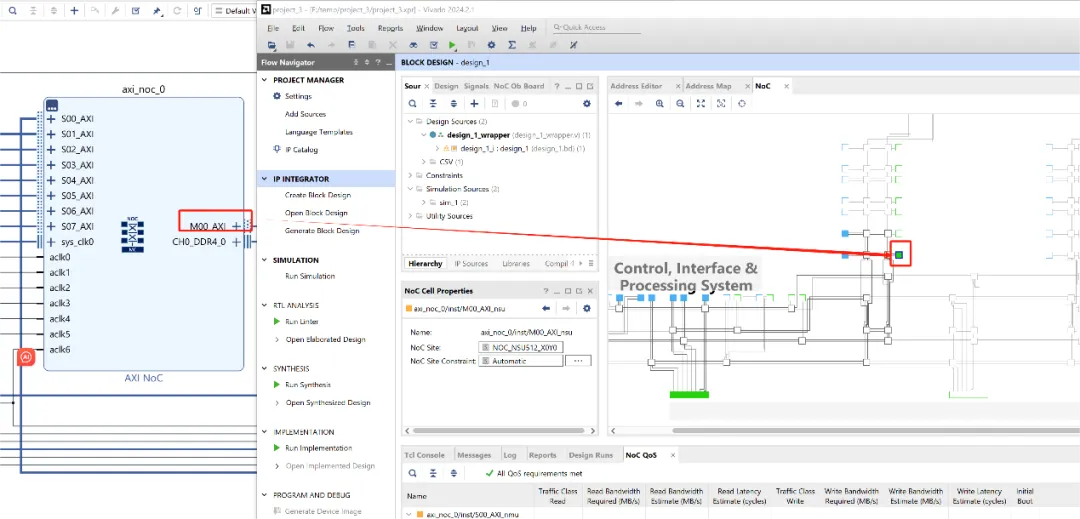

下图为Vivado工程中NMU的示例:

NMU内部结构:

当AXI请求进入NMU时钟域时,将执行数据分组,读写事务被分解为更小的传输(此过程称为chopping)。

NPP写入的最大大小为256字节。超过256字节的AXI写入可以跨越多个NPP写入。De-Packetizing&Packetizing会将粒度大于或等于256字节的事务切分为256字节的传输。例如,一个从0x0开始的1K传输事务将分为4 packet进行传输:0-255、256-511、512-767、768-1023。

Re-tagging模块在读取时重新标记以允许无序传输并防止互连阻塞。

在对外的AXI接口上支持配置32位~512位,在AXI4-Stream上支持从128位~512位的可配置数据宽度接口。AXI数据宽度通过参数传播从连接的IP,无需手动指定位宽。

2、NoC Slave Unit (NSU)

NSU的主要功能是接收和响应来自NoC的数据包,这些数据包寻址到NSU数据包接口,旨在发送到对应的AXI端口。

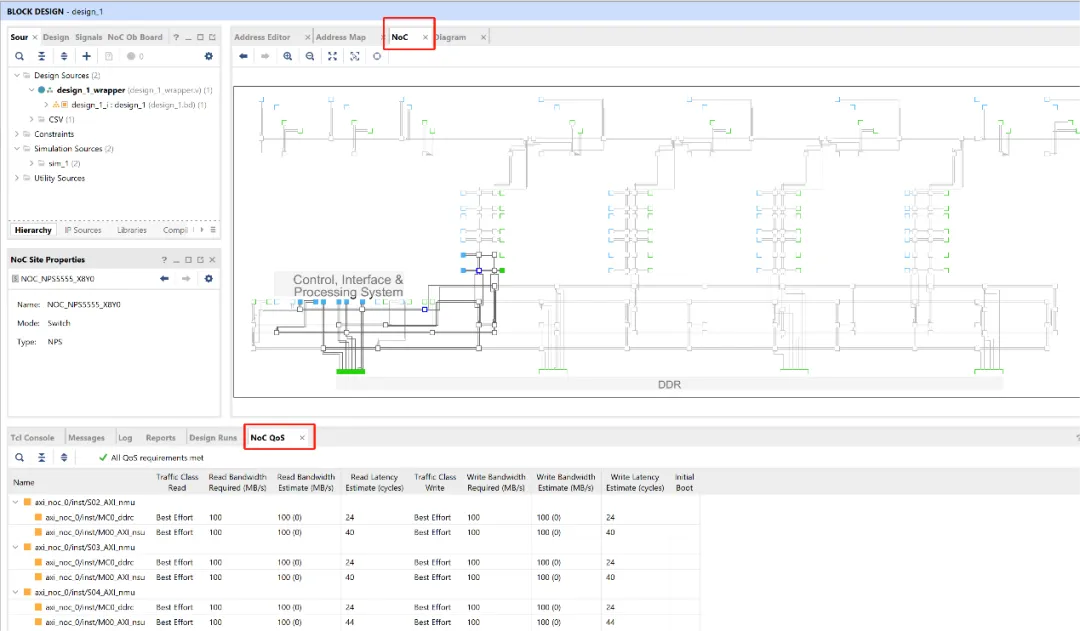

3、NoC Packet Switch (NPS)

连接NoC块以形成完整NoC网络交换。每个NPS都是全双工4x4 Switch,通过Switch至少有两个延迟周期。

NSU512(PL) NSU512(PL)

4、NoC Inter-Die Bridge (NIDB)

在多个SSIT芯片之间桥接垂直NoC(VNoC)。

Quality of Service(QoS)

Traffic Class与Read and Write Bandwidth

1、流量类别(Traffic Class)

定义了连接上的流量在NoC编译器和硬件中的优先级。流量类在NMU上设置,适用于从该NMU开始的所有路径。Traffic Class支持如下3种模式:

Low Latency:尽量减少结构延迟,DDR仲裁中优先级最高;

Isochronous:保证最大延迟;DDR队列中设定超时提前处理;

Best Effort:最低优先级,适合非关键流量。

2、带宽需求(Bandwidth Requirement)

单独设置读/写带宽(单位MB/s或Gb/s);

Vivado NoC Compiler会基于此进行资源分配与仲裁优化。

性能优化建议

关键流量优先保障:通过QoS将低延迟或同步流量优先级调高;

减少跨交换机跳数:布局时尽量缩短NMU→NSU的路径;

合理位宽分配:带宽与功耗需权衡,避免过度配置浪费资源;

多Die优化:跨Die数据尽量走专用VNoC通道,减少延迟;

路径可视化:在NoC Compiler拓扑图中检查关键路径是否经过不必要的节点。

在Vivado BD的NoC界面,可以看到DDR\NMU\NSU\NPS\QoS等。

点击如下QoS选择卡中的条目,可以看到此路径下的NoC拓扑。

文章来源:安富利