随着越来越多的数字芯片设计规模不断向着数十亿门迈进,FPGA原型验证作为芯片流片前的刚需验证环节,正面临三重核心挑战:超大规模设计下的编译分割效率低下;多FPGA级联场景的时序难以收敛;大规模信号调试的同步性与数据存储能力不足。

FPGA原型验证配套软件工具往往在“速率”与“debug深度”间难以平衡,成为项目开发周期的关键瓶颈。

在此背景下,亚科鸿禹结合丰富前沿用户工程应用实践,全面升级其VeriTiger®系列FPGA原型验证系统自动编译与深度调试全流程软件--hsPtCompiler2.0,以“网表分析引擎+自研分割算法”为核心,整合逻辑综合、分割、时序优化、深度调试与硬件管理全流程能力,为超大规模芯片FPGA原型验证提供高效、稳定的自动编译、实时管控、深度调试全流程软件解决方案。

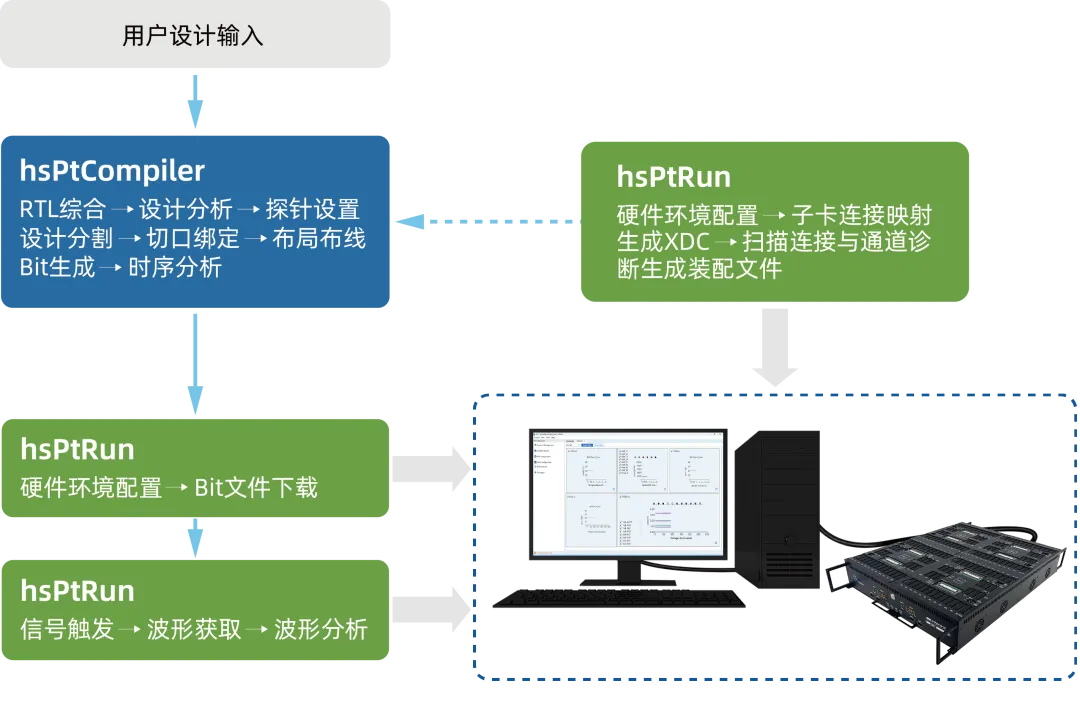

覆盖“编译-控制-调试”全流程

hsPtCompiler2.0由两大核心模块协同构成:

编译全流程模块--hsPtCompiler:专注于设计编译,集成了RTL综合、网表分析、分割、探针添加、P&R(FPGA布局布线)和时序分析等全流程功能。旨在高效处理大规模设计,优化时序性能,生成针对目标FPGA的Bit文件。

Runtime功能模块-hsPtRun:负责硬件环境控制与深度调试,支持原型验证平台登录、时钟电压配置、通道诊断,以及大规模信号的波形采集与分析,核心目标是“实时掌控硬件状态,实现深度调试”。

通过“编译优化+调试赋能”的协同设计,工具提供了从设计输入到硬件验证的全流程,避免多工具切换导致的效率损耗。

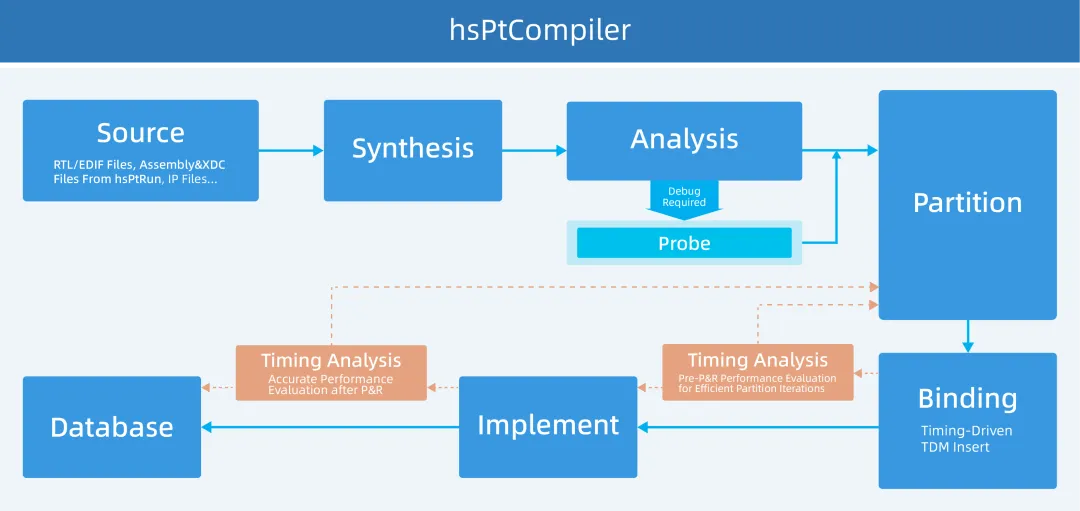

hsPtCompiler2.0 Work Flow

效率与性能双突破

hsPtCompiler: 超大规模设计“高效分割引擎”

针对数十亿门级设计的编译分割难题,hsPtCompiler模块通过多项核心技术实现突破:

数十亿门级可拓展:支持超128颗FPGA跨板级联,可灵活拓展验证容量,无需因设计规模超限而拆分验证任务。

RTL分割与时序驱动迭代优化:实现RTL分割流程,支持跨FPGA STA(静态时序分析),可结合P&R输出文件生成每片FPGA的SDF(标准延迟文件),精准计算上板后设计实际运行的最大频率;同时支持P&R前预估频率,提前规避时序风险。

多模式设计标准化网表生成:针对不同规模、不同层次的RTL设计,hsPtCompiler2.0构建了标准化的网表生成流程,高效融合不同模式设计文件,确保设计转化的准确性与灵活性,为后续的分割、P&R环节提供统一、可靠的输入基础;支持“Top-Down”和“Bottom-Up”两种综合模式配置,在验证的不同阶段可分别选用运行速度及FPGA利用率最大化或代码一致性及调试可视性最大化综合策略。

Bit文件多FPGA复用一键部署:在多FPGA级联验证场景中,多片FPGA承担完全一致的子模块验证任务非常常见,然而重复生成相同结构的Bit文件会占用大量时间。hsPtCompiler2.0内置Bit文件多FPGA复用一键部署功能,有效释放服务器资源,提升大规模硬件平台的部署效率。

自动构建关键模型与识别黑盒,多维度优化编译体验:三项自动化能力叠加,既降低了验证人员的操作门槛(无需手动梳理复杂设计),又缩短了编译周期,尤其适配包含大量第三方IP的复杂设计。

a) 自动构建时钟模型:自动识别时钟信号,生成精准的时钟树,为后续时序分析与优化提供基础;

b) 自动构建设计层次:自动生成可视化的设计层次结构,直观查看模块关联,便于手动设置分割约束或添加调试信号;

c) 自动识别黑盒:对设计中无需分析的黑盒模块(如第三方IP),工具可自动标记并跳过其内部编译流程,显著缩短整体编译时间。

时序驱动的TDM库绑定,以性能为目标优化硬件资源布局:通过时序驱动的TDM(时分复用)库绑定,自动扫描用户时序约束、识别时钟路径,智能指导硬件逻辑单元的选择,实现TDM库与逻辑设计的最优匹配,帮助设计在FPGA上实现更优的运行频率,从源头优化系统运行速度。

此外,hsPtCompiler2.0支持GUI和Script操作模式,全流程可分步调试,便捷高效。提供更灵活的分割性能调优,支持自动分割和用户手动分割模式进行性能优化,提供多种参数设置以快速达到预期分割效果。

hsPtCompiler流程框图

hsPtRun: 大规模调试的“精准控制中枢”

在硬件运行控制与调试环节,hsPtRun模块以“实时性、大规模、高带宽”为核心优势,解决传统调试工具的瓶颈:

硬件状态全掌控,环境配置更高效:支持USB、以太网两种方式连接原型验证系统,可快速完成硬件扫描、通道诊断;实时监控系统温度、电压、风扇转速,异常情况实时告警;多套件可批量上传或下载FPGA时钟、电压、Bit等配置,简化硬件环境设置流程。

16片FPGA同步采集,大规模信号深度调试:支持最大16片FPGA的同步采集,在单一界面同时调试16片FPGA,单片最大可追踪18K探针信号(含向量、数组形式),满足多片FPGA间大量探针信号同步调试需求。

超高存储容量与高速传输,数据采集更高效:外置64GB采样数据存储空间,不占用FPGA片上存储资源,搭配PCIe Gen3*8高速接口,波形数据传输效率大幅提升;采样频率最高可达140MHz,采样深度最高512M,可记录超长时间信号变化过程。

多通道信号添加,编译调试更高效:支持最高8通道添加信号,单通道最大数据位宽4K,可观测大量关键信号,无需重新编译,调试效率显著提升。

后门读写与虚拟IO功能,简化关键节点控制与监控:通过后门读写与虚拟IO功能,可直接访问用户设计中的AXI4外设(从设备),实现数据的快速读写交互;也可直接访问用户DUT(待测设计)的IO接口,用于“用户复位控制”(无需额外硬件触发)与“状态信号监控”(实时获取关键模块运行状态),无需修改RTL设计或重新编译,即可完成调试中的核心操作。

hsPtRun结构框图

后门读写方案框图

后门读写方案框图

核心价值

对于芯片设计团队而言,hsPtCompiler2.0的核心价值在于:

显著缩短验证周期:通过分布式并行编译、无需二次编译的探针添加、Bit文件复用等功能,减少重复操作时间。

提升验证可靠性:时序驱动的优化策略、跨FPGA静态时序分析、实时硬件状态监控,降低验证风险。

降低操作门槛:高度自动化的流程、多模式操作支持、直观的设计层次展示,让验证人员无需深入底层算法即可完成复杂设计的验证。

“hsPtCompiler2.0是我们深入前沿用户工程实践,直面超大规模IC设计编译调试的多重痛点,全面升级开发的自动编译、实时管控、深度调试全流程软件方案,强算法开发,在每个流程节点上深度探索系统性能、验证可靠性及自动化功能的协同提升。hsPtCompiler2.0将为前沿IC设计的FPGA硬件验证带来全新体验。”--亚科鸿禹 产品应用总监 于兆杰

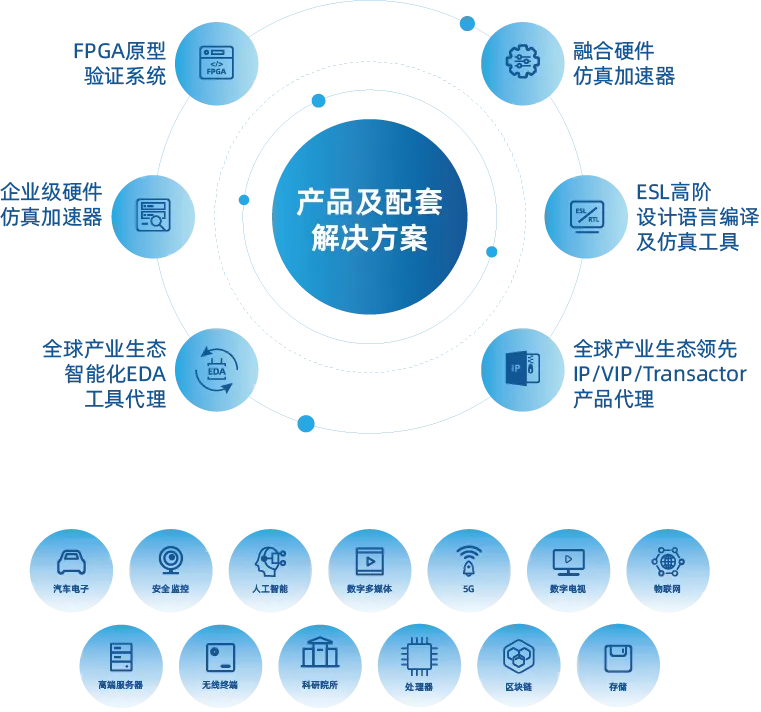

关于亚科鸿禹

亚科鸿禹团队于2009年成立,专注数字芯片功能验证EDA领域16年,是引领国产原型验证(Prototype)和硬件仿真加速器(Emulator)EDA工具研发和应用的先驱者。已推出八代原型验证产品和两代Emulator产品,全球累计用户超600家,赢得市场广泛好评和高度认可。

2020年总部落户无锡,成立无锡亚科鸿禹电子有限公司。获华大九天战略投资和全面支持,布局更多数字前端核心EDA工具,致力于成为“中国领先的数字前端EDA工具供应商”。

公司在北京、上海、合肥、西安设有研发中心,拥有近200人的人才团队,由具有20余年国际仿真验证从业背景的领域专家领衔,核心成员平均超过15年国内外知名EDA企业从业经验。公司与清华大学、合肥工业大学、江南大学等知名高校在EDA技术研发和人才培养方面保持长期产学研合作,共同推动国产EDA产业进程。

凭借硬核的行业基础和研发实力,无锡亚科鸿禹电子有限公司已获得"国家级专精特新‘小巨人’企业”、“国家级高新技术企业”、“国家级人才企业”、“江苏潜在独角兽企业”等国家级及省级荣誉,获批建设“无锡市数字EDA工程技术研究中心”、“无锡市企业技术中心”。

文章来源:亚科鸿禹