FPGA 设计开发过程中,软件是工程师必不可少的工具,好的软件开发环境可以简化设计者的设计流程,缩短开发时间,提升整体设计效率。

京微齐力2025福晞®软件工具,在旧版基础上结合其在 FPGA 项目的实际开发和应用过程中的综合表现进行多项优化和配置提升,从性能到时序,新版福晞®软件开发环境大大提升了工程师在 FPGA 设计过程中的效率和准确性。

京微齐力2025福晞®软件工具

设计性能优化

在 FPGA 设计领域,性能通常指的是电路在满足所有时序约束的前提下,设计能够达到的最高工作时钟频率,即通俗所说的 fmax,这也是衡量 FPGA 设计性能的核心指标。

实现时序收敛是设计开发过程中一个极其耗时的环节。如果设计的性能未能满足预期,可能需要进行多轮迭代优化,这将导致开发进度放缓,甚至出现延期。

为了克服这一挑战,我们对于2025版福晞®软件采取了一系列的优化措施。例如,开发了 retiming 算法来降低逻辑级数,挖掘 FPGA 架构的潜力以提高布局布线的灵活性。此外,此次优化还引入了 ixplorer 流程,该流程能够自动搜索合适的软件参数,进一步提升性能。

这些优化措施在基于 HME-P1 工业相机项目中取得了显著成效,在三个关键的时钟域(CPU、千兆网和 ISP)的 fmax 性能上,我们实现了15%至20%的提升。以下是三个不同型号的工业相机设计及其变种分别执行 ixplorer flow 后搜索到的最优结果,单位为 MHz。其中 183 设计的 lut 利用率为 69%,EMB 利用率为 85%。

软件运行时间优化

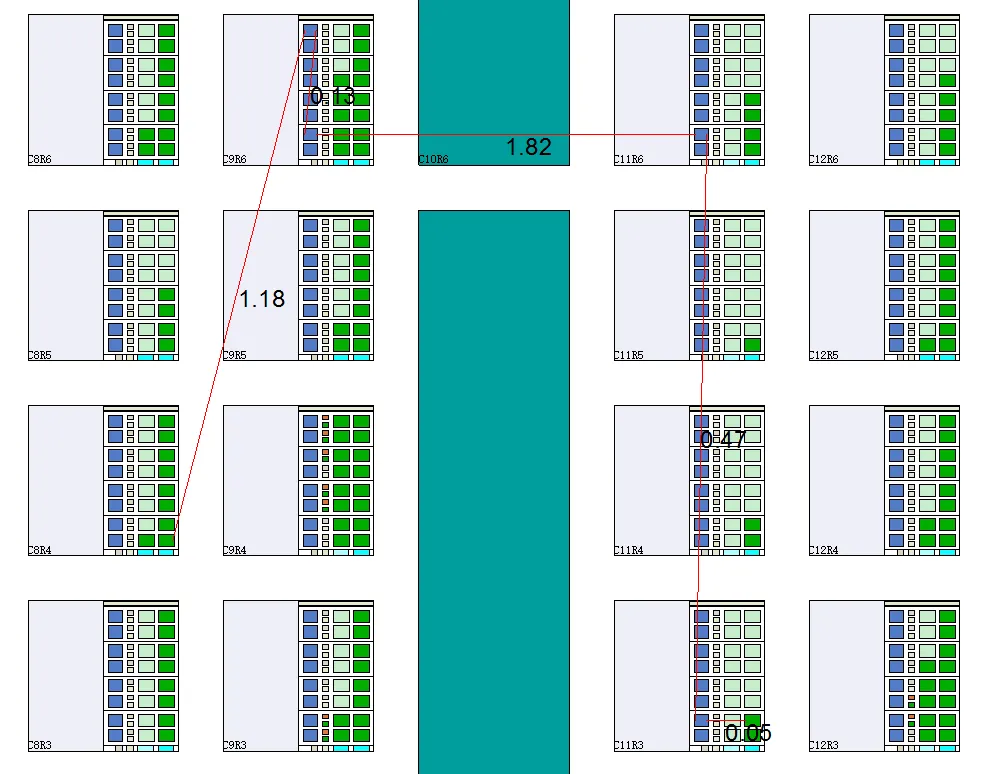

在 FPGA 的设计开发过程中,软件的运行时间直接关系到用户的设计体验和开发效率。尤其关键的是布线阶段,它往往占据了整个设计流程的大部分时间。为了解决这一问题,我们针对性的开发了相应的优化算法。通过优化综合后的网络拓扑结构、调整布局以降低拥塞,以及对布线算法进行深入优化,从而成功的显著减少了布线时间。

以下是我们部分测试结果的汇总:2025版本软件的布线时间约为2023年版本的36%,平均减少64%。大部分设计来源于客户提供的网表文件,少量设计来源于 intel 公开测试集。

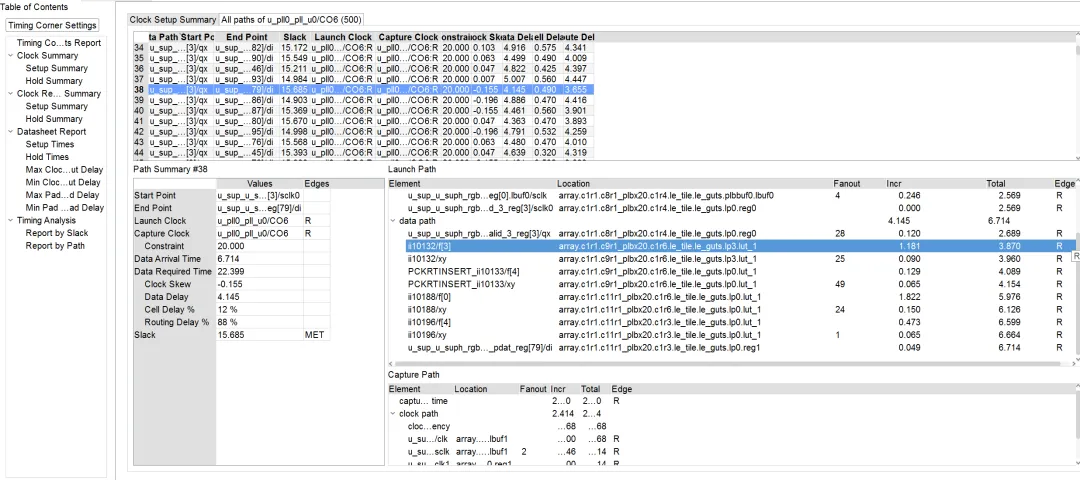

软件时序报告准确性优化

在 FPGA 设计开发过程中遇到问题时,进行时序违例检查是一种非常有效的诊断手段。一份精确的时序报告对于用户来说至关重要,因为它可以帮助工程师们迅速准确地定位问题所在。

为了提升时序报告的准确性,我们实施了一系列优化策略。包括采用 spice 仿真技术获取更精确的延时数据、进行上板实测来校准,以及在高低温环境下进行功能验证。此外,我们还收集了已量产设计的实际测试环境。

我们进一步引入了 ixplorer 流程,生成了多个运行结果,并对这些结果进行了逐一验证,以确保时序报告的准确性。以下是我们收集到的测试环境设计列表:

基于 HME-HR03 芯片的屏显设计:为屏显技术提供精确的时序验证。

基于 HME-H3 的屏显设计:进一步增强了我们对屏显设计时序问题的理解。

基于 HME-P0 的 LED 接收卡设计:针对 LED 接收卡的特定需求进行时序分析。

通过这些综合措施,京微齐力致力于为用户提供更为可靠和精确的时序报告,以优化用户、工程们的开发体验。

文章来源:京微齐力