作者:Zhang Cheng,AMD开发者;来源:AMD开发者社区

在上一篇Blog基于XPHY构建源同步接口(一)中主要阐述了XPHY的内部结构以及实现源同步接口的基本原理。本文将建立测试工程并且通过仿真进一步介绍Versal XPHY的相关特性。

1.Example design工程架构

基于example design工程开始新的设计可以快速搭建原型并验证功能,为了更方便做后续上板测试,需要对example design做一定的修改。example design的结构主要包括几个部分。

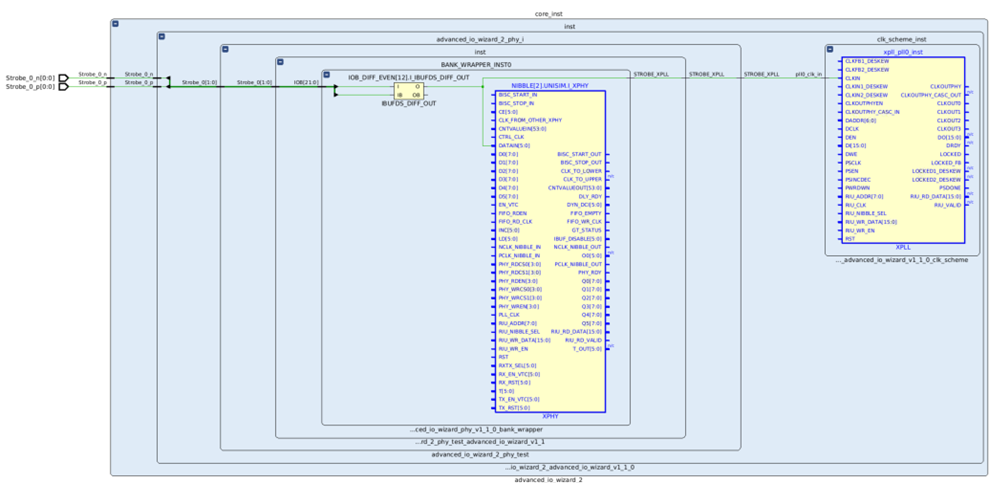

core_inst: RX 接收模块;

exdes_inst: TX 发送模块,如果生成的是 RX IP 实例,示例设计中会创建一个 TX IP 实例并进行回环。TX的设置会与RX保持匹配,比如线速率、通道数量、同步或异步、Center DDR或Edge DDR等方面;

clk_wizard_core: MMCM模块,为RX提供PLL时钟;

clk_wizard_ex: MMCM模块,为TX提供PLL时钟;

clk_wizard_ctrl: MMCM模块,提供ctrl_clk时钟;

I_PRBS_ANY_GEN: PRBS码生成模块,当数据对齐后,TX 端会发送 PRBS测试码, RX 端的 PRBS 检查器会检查数据完整性。

2.时钟

a. 时钟物理约束

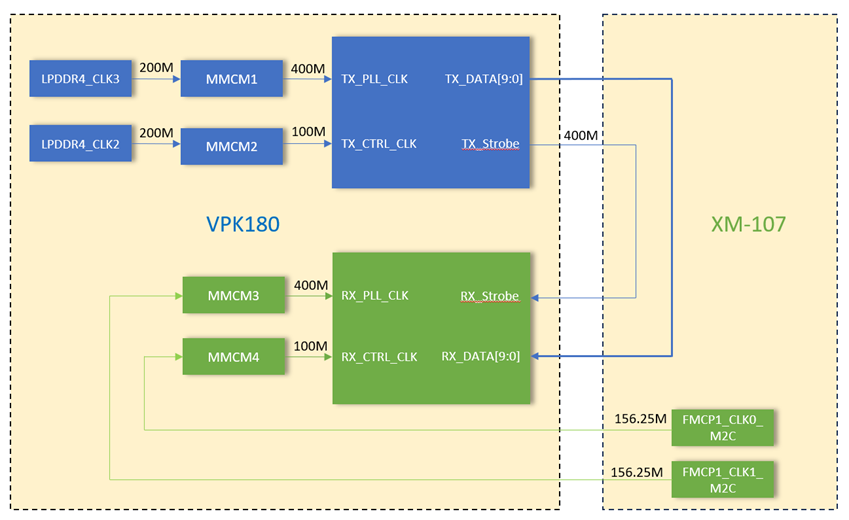

后续上板测试将基于VPK180评估板和WHIZZ XM-107环回模块,这里需要按照实际板子上的时钟频率做相应的修改。为了保证TX和RX使用非同源的时钟,这里TX的时钟都使用VPK180的时钟源,而RX则使用XM-107上的时钟源。因此,TX提供PLL时钟的MMCM输入时钟修改为200M,IO类型为差分,这个时钟将被约束到VPK180的LPDDR4_CLK3。RX的MMCM时钟修改为156.25MHz,IO类型为差分,这个时钟将被约束到FMCP1_CLK0_M2C,由XM-107 loopback卡提供时钟。修改后的时钟结构如下图所示:

b. 时钟配置说明

TX和RX都需要有两个时钟输入,分别是CTRL_CLK和PLL_CLK。

CTRL_CLK:复位状态机和 XPHY nibble 模块的时钟,可以外部输入也可以将内部PLL 的 Clkout1 输出用作 CTRL_CLK。

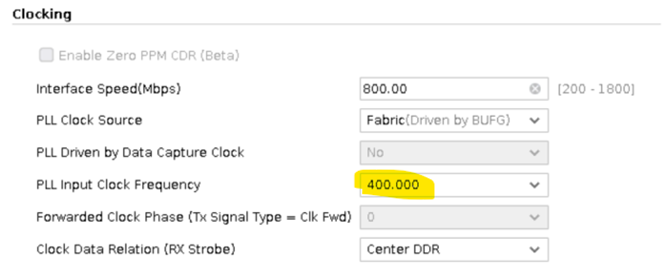

PLL_CLK:XPLL的输入时钟,输入的频率值需要与Wizard中的设置保持一致。

PLL Clock Source: 可以选择从外部时钟管脚输入或从内部BUFG输入。

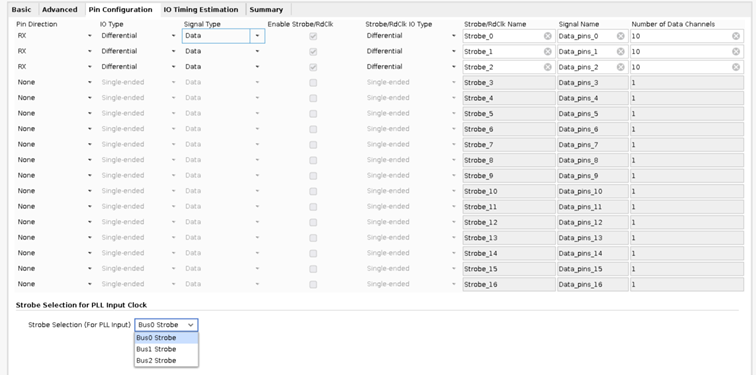

如果选择从外部时钟管脚输入,还需要指定是否将Strobe输入用作PLL的时钟源,它们之间的差别是如果PLL时钟使用Strobe输入,那么IP 会将所选的 Strobe 信号同时连接到 XPLL和XPHY。如果PLL时钟不使用Strobe输入,那需要额外提供XPLL的时钟。

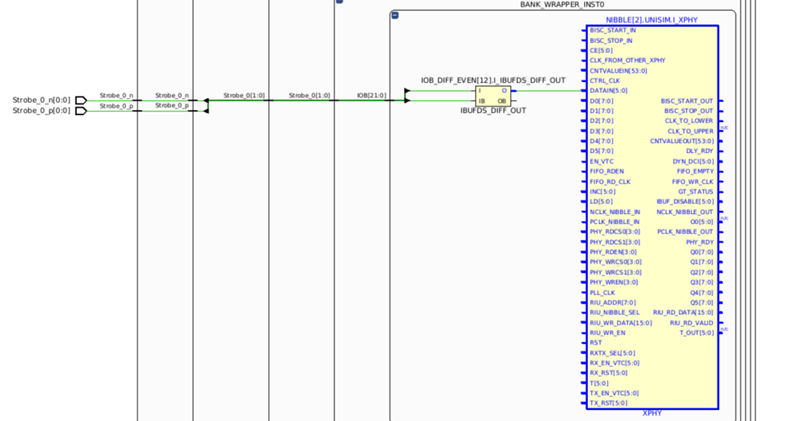

PLL Driven by Data Capture Clock = Yes, Strobe信号同时连接到 XPLL和XPHY,如下图所示:

当选择了多行、多 Strobe 或多个功能时,IP 会另外要求选择一个连接到 XPLL 输入的 Strobe。在Strobe Selection for PLL Input Clock页面中选择Strobe的位置,这里选择的Strobe会被同时连接到XPLL和XPHY。对于多 bank 设计(如 3-bank 设计),所选择的 Strobe 必须放置在中间的 bank,这样相邻的 XPLL 才能访问该 Strobe,并获得最佳布局。

PLL Driven by Data Capture Clock = No, Strobe 信号只连接到XPHY,如下图所示:

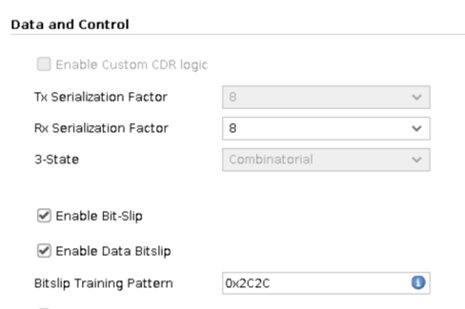

3.训练码和数据流

为了便于观察接收数据,在初始化完成后,TX持续发送0x2C2C的训练码,用于Bit位对齐;对齐完成后,通过发送发送0x0000000000-0xFFFFFFFFFF循环的数据代替PRBS Pattern。这里需要移除I_PRBS_ANY_GEN: PRBS模块,增加下面的代码。

always @(posedge core_rx_clk) begin

if(bitslip_sync_done & core_intf_rdy_t)

data_from_fabric_ex_Data_pins_0 <= data_from_fabric_ex_Data_pins_0 + 1'b1;

else

data_from_fabric_ex_Data_pins_0 <= 80'h2C2C2C2C2C2C2C2C2C2C;

end

增加VIO控制start_bitslip便于上板测试,同时监控bitslip_sync_done,ILA监控RX端的并行输入数据data_to_fabric_Data_pins_0。

4.Testbench

因为工程做了相应的简化,在仿真时只需要在Testbench中添加三个功能:

a. 将TX数据环回到RX端(n端相同操作)

assign Strobe_0_p = ex_clk_fwd_p;

assign Data_pins_0_p = ex_Data_pins_0_p;

b. 为RX端提供时钟(n端时钟相同操作)

always

begin

# (6.400000/2) core_clk_p = ~core_clk_p; //156.25 MHz clock

end

always

begin

# (6.400000/2) core_ctrl_rx_clk_p = ~core_ctrl_rx_clk_p; //156.25 MHz clock

end

c. 为TX端提供时钟(n端时钟相同操作)

always

begin

# (5.000000/2) ex_clk_p = ~ex_clk_p; //200 MHz clock

end

always

begin

# (5.000000/2) core_ctrl_tx_clk_p = ~core_ctrl_tx_clk_p; //200 MHz clock

end

5.仿真结果

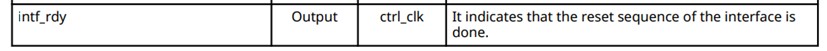

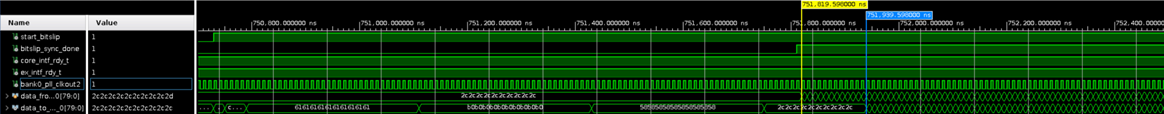

a. 运行仿真直到core_intf_rdy_t和ex_intf_rdy_t这两个信号置1,这两个信号分别代表TX和RX两个IP初始化完成。

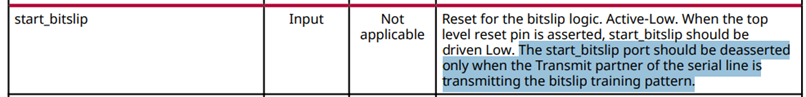

b. 右击start_bitslip,选择force constant,将这个信号强制置1,等待bitslip_sync_done置1完成bit位对齐,注意在bit对齐后还需要继续保持start_bitslip为1。只有在复位和TX发送训练码的时候才将start_bitslip置0。

发送的训练码需要与wizard中的Bitslip Training Pattern设置保持一致。

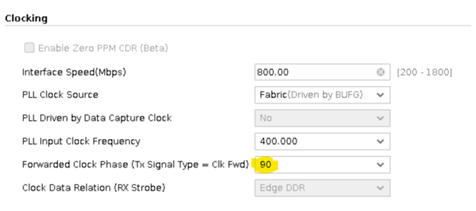

c. TX端的Forwarded Clock Phase控制时钟和数据的对应关系,有两种参数可选,本工程使用中心对齐模式。

0:数据与时钟边沿对齐

90:数据与时钟中心对齐

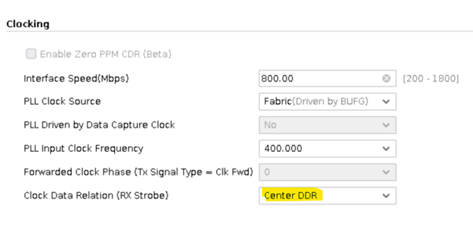

d. RX端的数据对齐在下方clock data relation的位置设置,也是两种模式。

e. 串行数据如下图所示,在黄线和白线之间为1个字节的数据(0x2C),数据格式为低位在前,高位在后。

f. 完整的仿真结果:

下一篇Blog将上板实测工程。