作者:Carey Huang,文章来源:骏龙科技社区

本文主要介绍 Altera FPGA 外部存储器接口 EMIF 的技术选型、设计实现、仿真验证与硬件调试。

Altera FPGA EMIF 简介

EMIF,全称 external memory interface,是 Altera FPGA 中用于连接外部存储器的专用接口控制器,当前支持系列有 20nm 的 Cyclone® 10GX、Arria® 10GX/SX;14nm 的 Stratix® 10 全系列和 Agilex® 5 全系列、7nm 的 Agilex® 7 全系列。EMIF 目前支持的协议如下:

DDR5、LPDDR5

DDR4、LPDDR4

DDR3、LPDDR3

QDR II、QDR IV

EMIF 结构与特点

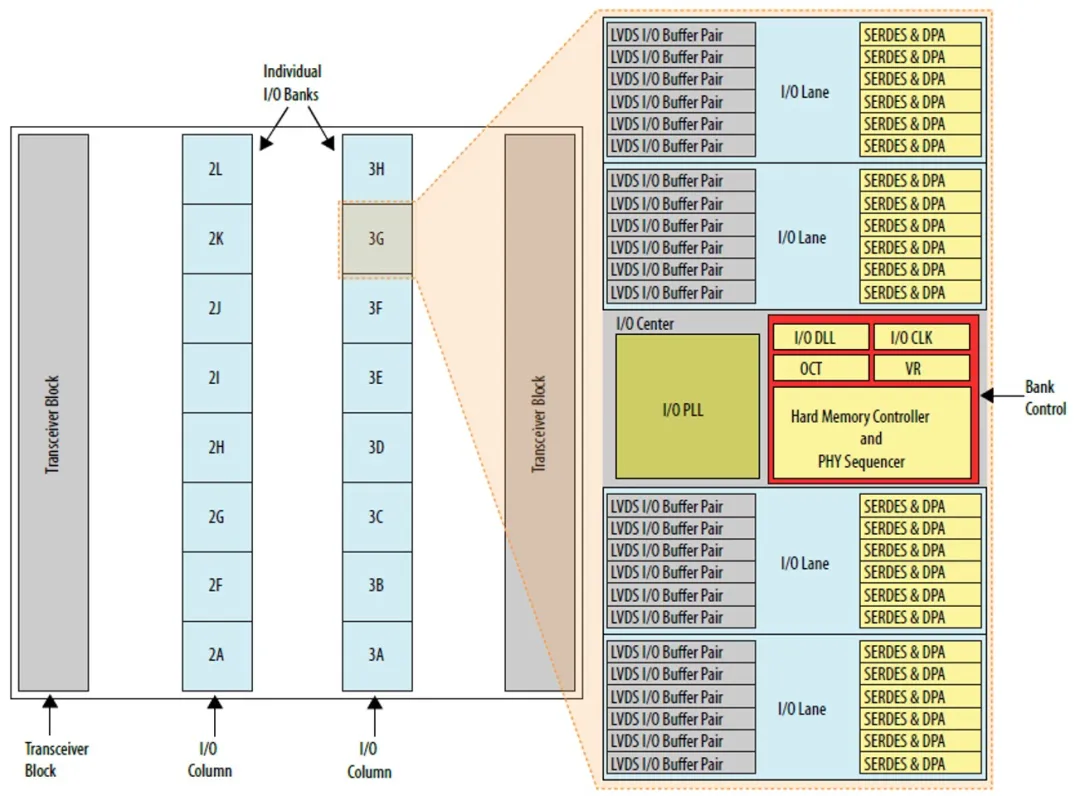

EMIF 的核心结构如下:几乎每个 IO Bank 都会有 EMIF 硬核控制器(Agilex® 系列是两个,其他系列是一个),每个 IO Bank 的 EMIF 主要相关模块有做校准的 Hard Sequencer,做 DDR 时序控制的 Memory Controller,做 High-Speed PHY Clock Tree,做时钟相位对齐的 Clock Phase Alignment。

图1 IO Bank 结构

图2 IO Bank 中 EMIF 相关模块

EMIF 具备以下三个显著特点

专用存储器存放校准算法代码,由片上晶振提供时钟源,确保时序精度。

预留调试接口,可与 Quartus Prime Debug Toolkit 等工具对接,便于系统级调试。

IO-AUX 模块专门用于存储器接口校准,该模块为硬件专用,用户无法直接调用。

下图(图3)罗列了 EMIF 支持的类型:

图3 EMIF 支持类型

芯片选型与带宽评估

在选择 FPGA 芯片时,需根据存储器接口的带宽需求进行评估。Altera 提供了以下两个实用工具:

1. EMIF 设备评估表

确定实现预期带宽所需的内存接口

根据所选的内存配置计算带宽

显示支持所选内存接口的所有 Altera Agilex®、Altera Stratix® 10 和 Altera Arria® 10

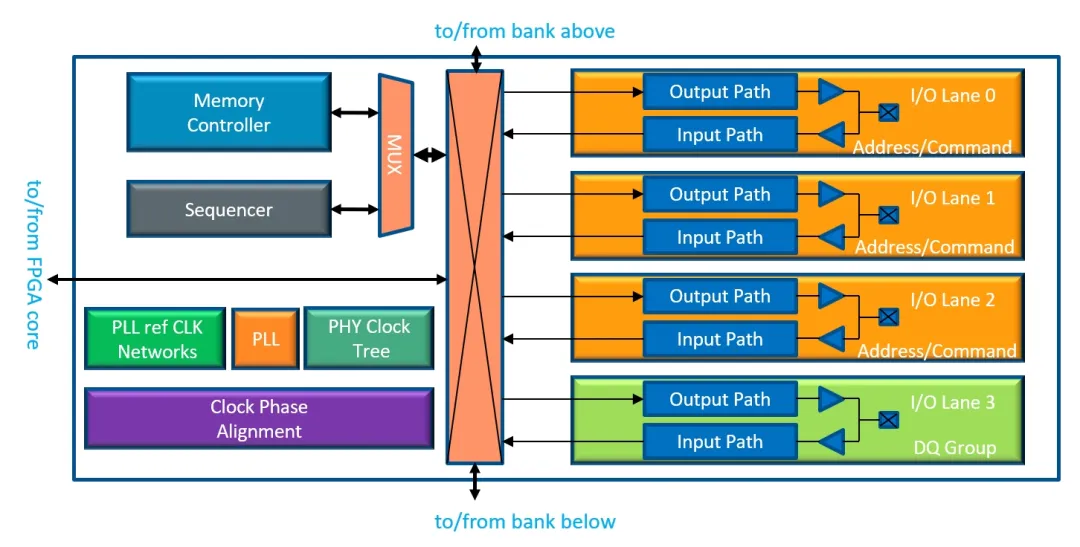

2. EMIF 规范估算器

确定实现预期性能所需的 Altera FPGA 设备产品家族和速度等级

显示不同内存选择所提供的最大频率和 DQ 宽度

推荐访问:Altera EMIF 支持页面

图4 设备评估表

图5 网页估算器

EMIF 设计要点

I/O Lane 配置

I/O Bank 的一个 Lane 可以用作一个 x8/x9 的 DQ 组,包括一对 DQS/DQS# 和最多 10 根数据线(包括 DQ 和 DM);当然也可以把一个 Lane 用作两个 x4 的 DQ 组,这种情况下有两对 DQS/DQS# 和 8 根 DQ,不支持 DM;还可以用多个 Lane 构成 x18 和 x36 的 DQ 组。

图6 I/O Lane 配置示意图

需要注意: 在一组 DQ 中,DQS 位置基本是固定的,多为 DQ 组的中间,以保证信号完整性 在一组 DQ 中,DQ 的顺序可以调换,正常 fitter 都能通过 一个 Lane 里,使用 DQ 组后,剩下的 IO 可以作为普通 GPIO 使用

AC 信号布局

对于 AC 信号(Address/Command),每个信号都有其固定的位置,不可随意摆放。

图7 AC 信号布局示意图

对于跨 Bank 的 EMIF,需保证 IO Bank 是连续的,AC 信号要放置于信号簇的中间,且 AC 信号不能跨 Bank。 Bank 区不连续的地方不能组合一个 EMIF 设计 不同列的 Bank 不能组合一个 EMIF 设计

图8 跨 Bank EMIF 的 AC 信号布局示意图

在 HPS 的 EMIF 设计上,Bank 位置是固定的

A10 HPS 的 EMIF 里,I/O Banks 2K 和 2J 用于 x32/ x40 设计,2K、2J、2I 用于 x64/x72 设计

AC 信号簇和 ECC 数据都要位于 2K Bank

PLL 参考时钟、RZQ 信号必须位于 2K Bank

在单个数据通道内(实现单个 x8 DQS 组):

- DQ 引脚必须使用序号 1,2,3,6,7,8,9,10 的引脚。DQ 位之间可以交换位置(例如可以交换 DQ[0] 和 DQ[3] 的位置),只要结果引脚只使用规定的这些序号引脚

- DM/DBI 信号必须使用序号 11 的引脚

- DQS/DQS# 必须使用序号 4、5 的引脚

IP 配置与仿真

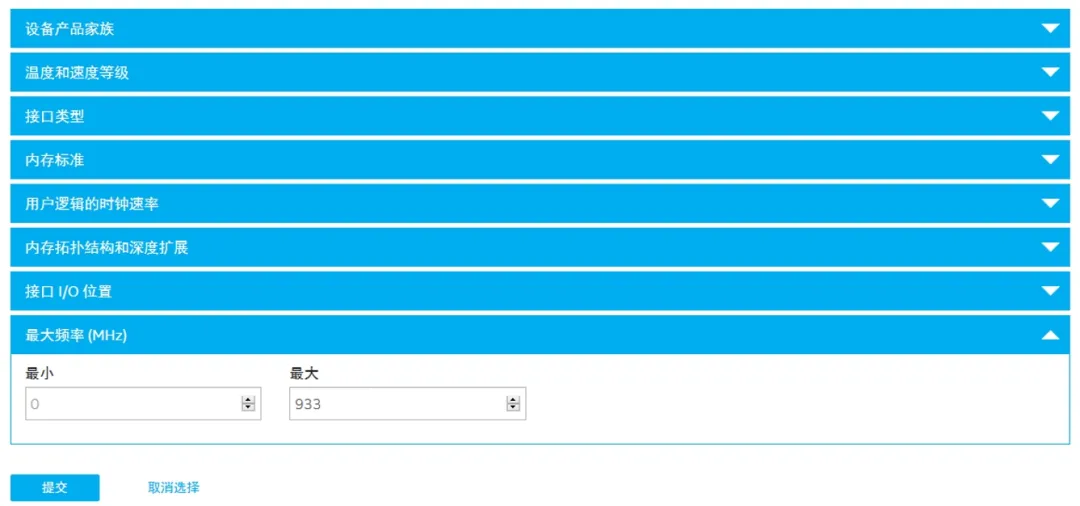

接下来介绍 IP 配置与仿真。根据下图(图10)操作先选择需要用到 DDR 类型,再生成 example 工程。

图9 加载 example 配置

图10 设置 DDR 参数

图11 设置时序参数

图12 修改板级参数

图13 设置仿真与调试参数

仿真选择

建议跳过校验、使用隔离 PHY,以提升仿真速度。

勾选 Simulation,选择仿真语言格式。

使用 EMIF 生成的 Example 在 Modelsim 上进行仿真

图14 仿真流程

其他仿真平台请参考“External Memory Interfaces Altera Arria® 10 FPGA IP Design Example User Guide”文档。自建工程仿真时,需要在 IP生成时选择生成仿真文件,然后在搭测试环境时就可以在测试文件里添加 example 时生成的 DDR 仿真模型,或者到 DDR 原厂网站下载对应型号的仿真模型进行添加。

硬件调试与故障排查

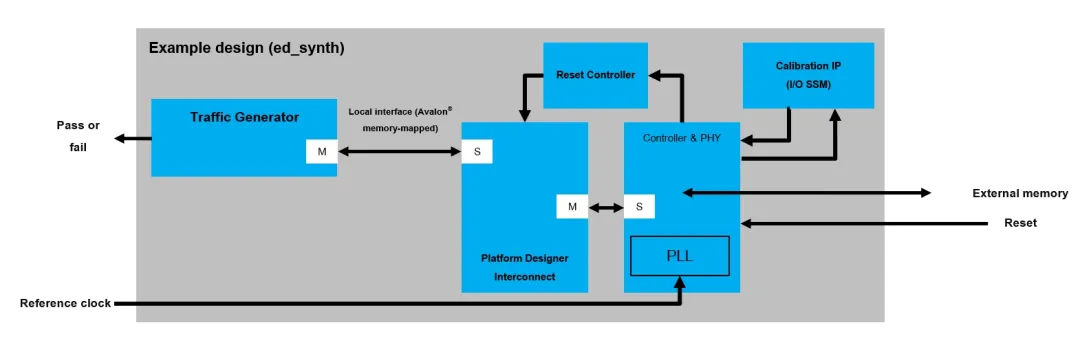

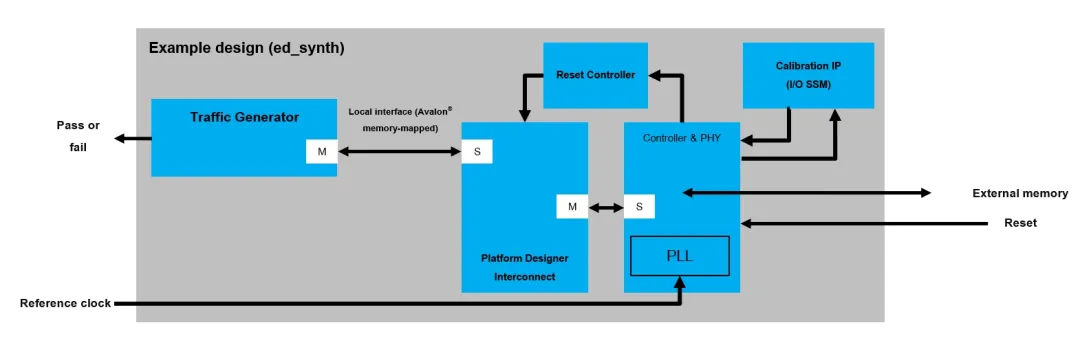

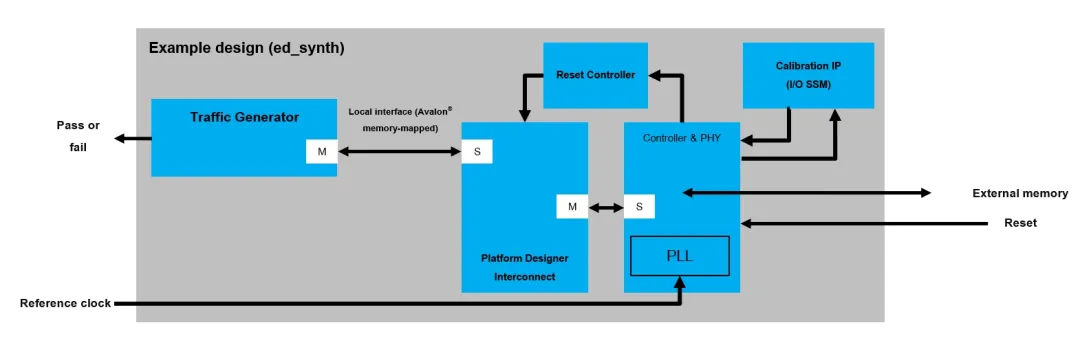

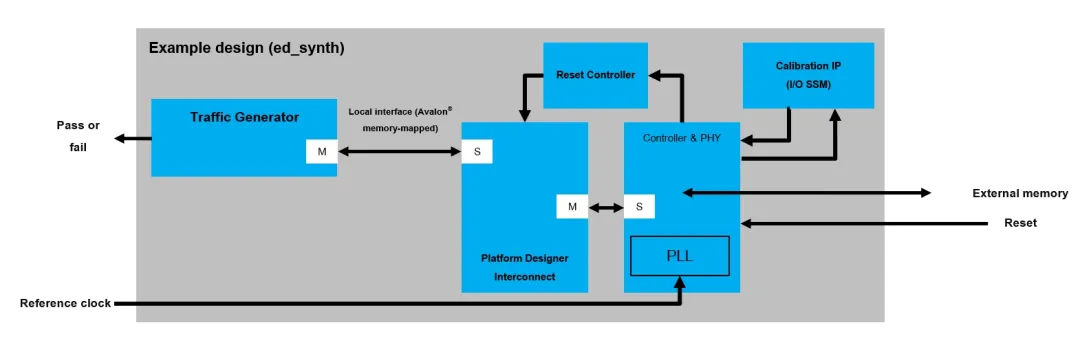

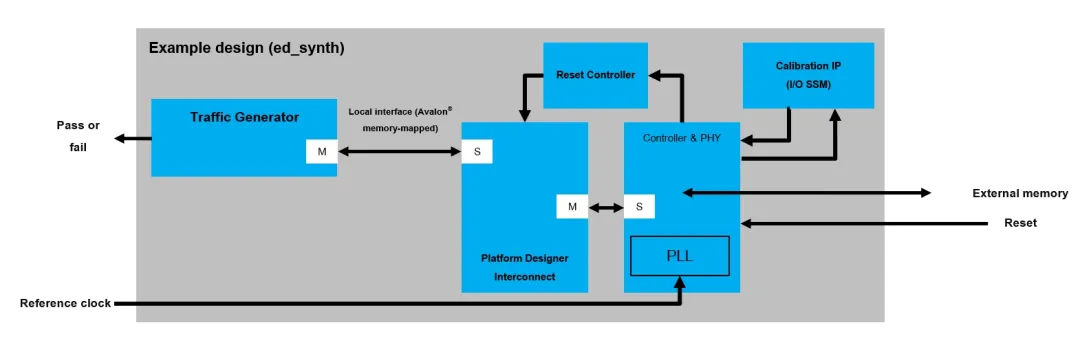

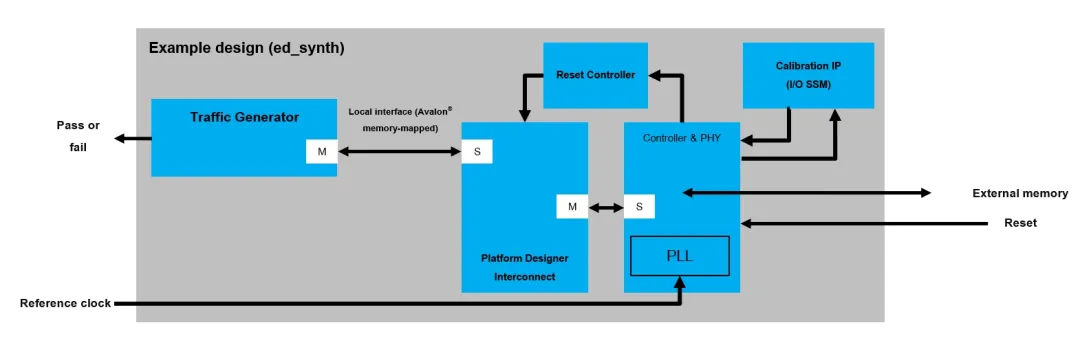

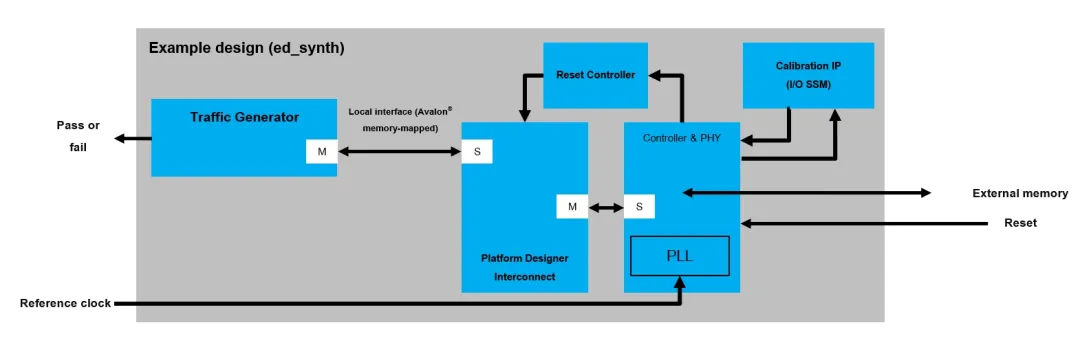

在做 memory 的调试时,建议优先使用 IP 生成的 example 进行测试,该 example 里头有着丰富的样本与指示信号,便于调试。

图15 EMIF 调试系统框图

下图(图16)为硬件检查清单:

图16 硬件检查清单

当出现校准失败或有误码时,可参考以下方向进行排查:

检查 DDR 端电压、VREF、FPGA IO Bank 电压、FPGA 侧 VREF 等是否在要求范围里;

检查 FPGA 与 DDR 端的 RZQ 电阻值是否焊接 240Ω;

检查 IP 里 memory timing 栏参数是否与颗粒手册要求的一致;

在手册要求范围内,加大 CWL 和 CL 的值;

查看 Quartus report,看报告是否有时序违规,消除违规;

降低 memory 的数据速率;

减少控制的颗粒数量;

对于 DDR3L 可尝试把电压抬升到 1.5V;

……

使用 Signal Tap 与 Debug Toolkit

Altera 的 EMIF IP 设置完参数后均可生成一个 example,所有样机调试都可以通过这个 example 来调试,可以通过 signal tap 抓取以下信号进行分析指导:

Local_cal_fail:校准失败

Local_cal_success:校准成功

Traffic_gen_fail:有误码

Traffic_gen_pass:没误码

Pnf_per_bit:指示当前数据位置是否错误

Pnf_per_bit_persist:指示整个测试流程当前位置是否发生过错误

Avalon-mm:逻辑与 IP 的数据交互接口

运行Debug Toolkit

点击 “Initial Connections”

点击 “Link Project to Device”

点击 “Create Memory Interface Connection”

可选点击 “Create Efficiency Monitor” 查看效率

点击 “Report Calibration” 获取校准报告

校准报告

各 DQS 组校准状态

DQS 信号的延时校准数据

2D 眼图(静态显示,可用于初步判断信号质量)

总结

Altera FPGA 的 EMIF 接口为高性能存储器连接提供了完整的硬件与软件支持。从芯片选型、IP 配置、仿真验证到硬件调试,每个环节都有相应的工具与方法论支持。建议在设计初期就充分利用官方工具进行评估,并在调试阶段善用 Example Design 与 Debug Toolkit,可显著提升开发效率与系统稳定性。