在技术飞速发展的今天,内存性能、占用面积和能效已成为现代应用的关键考量因素。

Agilex™ 5 FPGA 内存技术提供灵活的内存接口,可有效应对上述关键需求。

Agilex™ 5 设备支持 DDR4、LPDDR4、 DDR5 和 LPDDR5,不仅紧跟行业新标准,还能降低工作电压、功耗以及单位比特总成本。这些内存技术与 Altera FPGA 深度集成,可有效赋能 4K/8K 视频视觉处理、AI 图像分类、数据库以及数据分析等应用加快数据处理速率并优化能效。

为助力用户针对具体应用场景选择合适的 DRAM 解决方案,下文将阐述不同类型 DRAM 的关键差异化特性。文中结合 Agilex™ 5 设备的外部内存支持能力,重点分析了 Agilex™ 5 设备的 I/O Bank 相较于前代产品及市面上类似产品的核心突破。

此外,本文还探讨了 Agilex™ 5 E 系列外部内存的实际应用案例,重点突出了其相较于市面上类似产品的核心优势。以搭载 Warp IP 的 4K 多传感器摄像头解决方案为例,该方案实现了以下成果:

从 DDR4 迁移至 LPDDR5 后,功耗降低了约 41.2%;

与市面上类似产品的 DDR4 解决方案相比,功耗降低了约 47.4%;

与市面上类似产品相比,Agilex™ 5 设备的总功耗降低了约 28.6%。

专用 DRAM 的演进与应用

随着 DDR 技术的演进,SDRAM 分化出移动内存(即具备更低功耗的 LPDDR)和图形内存(即 GDDR)两大类型。

尽管 GDDR 仍主要专用于图形处理领域并仅在部分场景中被重新用于 AI,但其“同门师兄” HBM (包括 HBM2 和 HBM2e)正因市场对以更低能耗 (pJ/bit) 实现更高性能的迫切需求而迅速发展。

高带宽内存不再只针对 AI 和科学计算领域,其在有线网络数据包缓冲和快速查表等网络应用中也变得愈发关键。

选择合适 DRAM 的关键要素

在选择 DRAM 时,以下特性是决策的关键考量因素:

• 容量

DDR5 和 DDR4 提供最高容量,每个设备中 DDR 的容量是 LPDDR 的4倍。单个 Dual-rank DDR5 DIMM 的容量可达 256 GB,是单个 HBM2e 堆栈的 16 倍。

• 成本

HBM 虽然价格最高,但包含功耗成本在内的 TCO 可能是影响决策的一项关键因素。

对于 DDR4、DDR5、LPDDR4 和 LPDDR5 而言,其成本及单位比特成本 (cost per bit) 会随着技术成熟度与市场需求的变化而波动。小型 LPDDR 设备的成本可能与大型 DDR 设备的成本相当。HBM 虽然价格最高,但从其整个生命周期的 TCO 来看,可能更具成本效益。

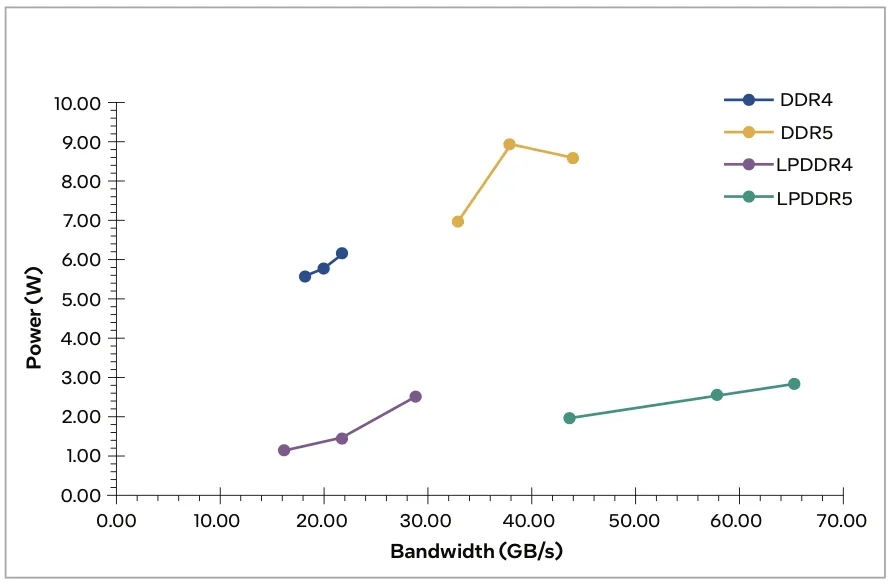

DDR4/5 与 LPDDR4/5 x64 位宽接口的单位带宽功耗示例

• 能效与每瓦性能

HBM 在峰值带宽和每瓦性能方面表现突出。DDR5 与 LPDDR5 可提供相近的带宽性能,但 LPDDR5 的能效更高,其 VDDQ IO 摆幅为0.5 V,而 DDR5 则需要 1.1 V。LPDDR DRAM 阵列比 DDR 更小且能效更高。随着先进技术节点的发展,其能效有望得到进一步优化。

关键结论是:LPDDR5 在绝对功耗和每瓦性能两方面均具备明显优势。不同 DRAM 阵列的功耗差异显著,选择不同的内存方案将直接影响解决方案的整体功耗水平。

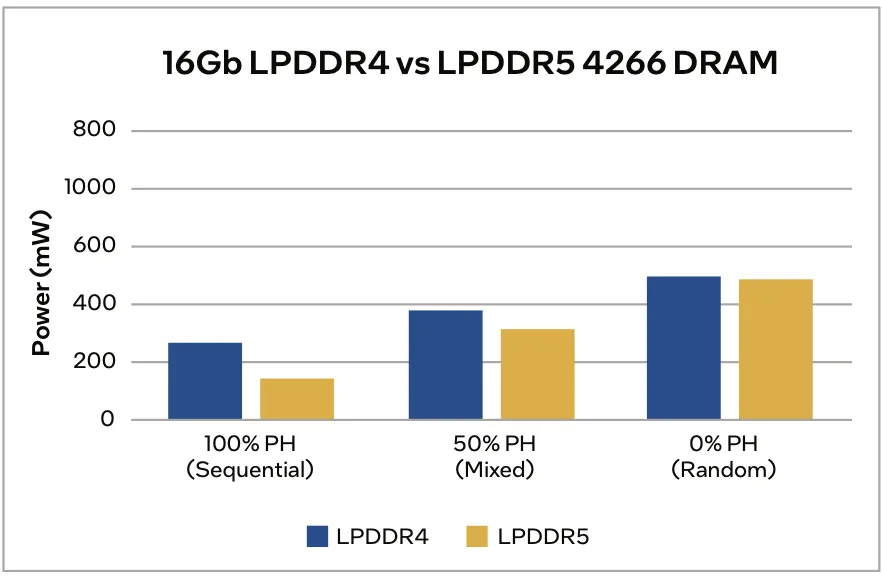

下图展示了不同 DRAM 访问模式对功耗的影响。顺序访问模式或高页命中率(High PH)意味着 DRAM 页(或行)保持打开状态的时间更长,从而避免了因关闭旧页(预充电)和打开新页(激活)而产生的功耗损失。

Bank Grouping 技术的引入提升了 LPDDR5 的整体能效表现,但在随机访问场景中,结构更简单的 LPDDR4 仍可实现与之相近的功耗水平。

DRAM 访问模式影响阵列功耗

• 带宽与实际吞吐量

高带宽内存在吞吐量方面优势显著,但与前几代产品相比,DDR5 和 LPDDR5 能为成本敏感型解决方案提供可观的性能提升。理论峰值带宽并不能完全反映实际性能,访问模式也至关重要。顺序访问可避免因开启与关闭行 (row) 而带来的性能损耗,而更长的突发长度 (burst length) 与通道化 (channelization) 设计则能提升效率。

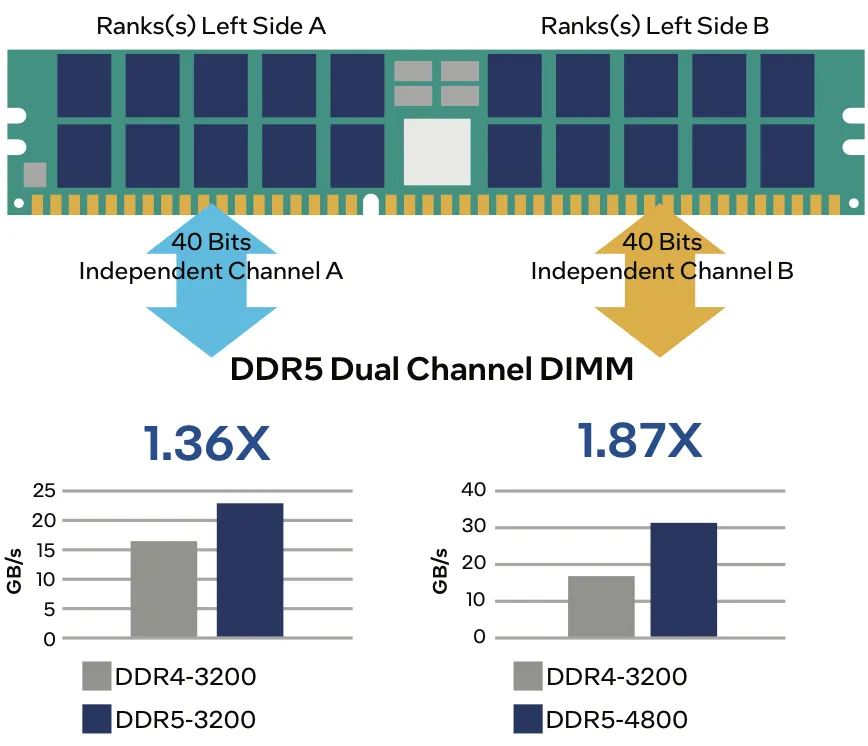

DDR5 采用双 x32 宽通道设计和 16-beat 预取机制。这使得 DDR5 通过 x32 接口即可实现 64B 缓存行访问,从而提升带宽。如下图中的美光 (Micron) 数据所示:在随机 64B 访问场景下,DDR5 的有效带宽较 DDR4 提升了 36%,并能在速度小幅提升的情况下实现明显的性能增益。

美光对比 DDR5 与 DDR4 实际吞吐量

Agilex™ 5 外部内存与 I/O 能力

Agilex™ 5 设备是业界较早同时支持 DDR4、LPDDR4、DDR5 和 LPDDR5 四种差异化外部内存解决方案的产品之一。且 Agilex™ 5 设备的高速 I/O 还原生支持 MIPI D-PHY,速率高达 3.5 Gbps。

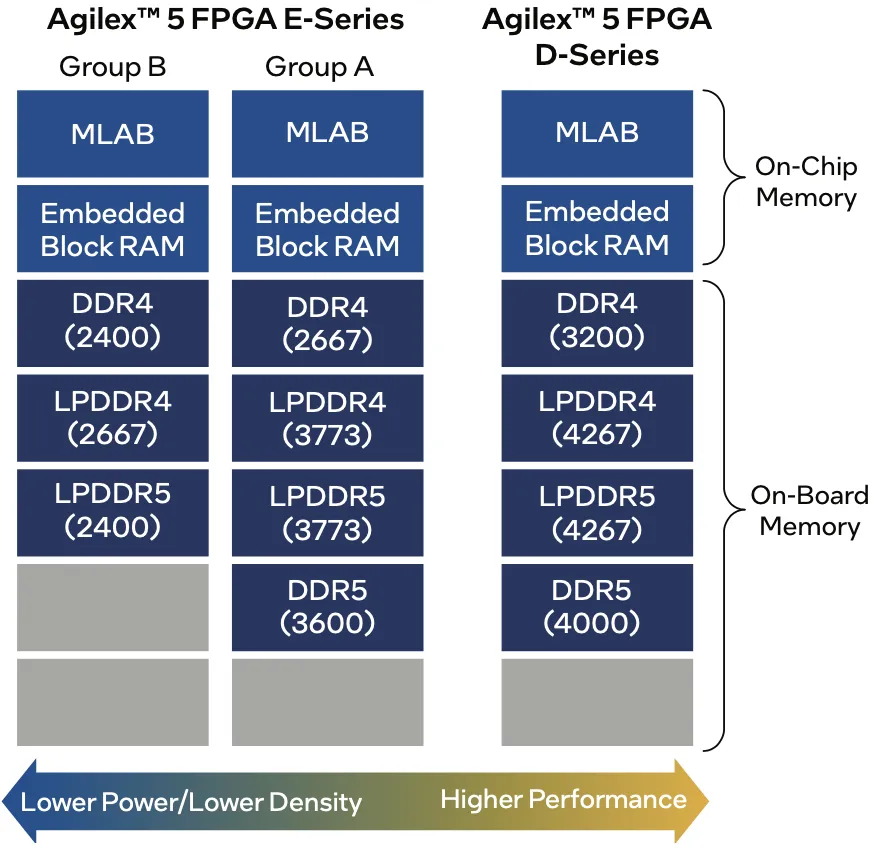

Agilex™ 5 家族产品的内存支持方案

Agilex™ 5 设备 I/O Bank 概述

• 每个 I/O Bank 的关键特性

1. 双硬核 DRAM 控制器

• 32 级深度的读/写命令队列

• 双 16 位或单 32 位宽通道

• 面向用户逻辑的 AXI-4 接口

• 按 Bank 刷新

• 丰富的 RAS/调试功能

- SECDED ECC

- LPDDR5/5 带内 ECC

- LPDDR5 链路层 ECC

- ECC 回写

- 按需清理

- 控制器与DRAM BIST及配套调试工具包

- 用于性能调试的遥测计数器

- Dual-rank UDIMM、RDIMM和SODIMM

2.支持 MIPI、LVDS、PHYLite 和通用 I/O (GPIO),并具备高效的引脚封装

• 每半个 Bank(48 个I/O)支持独立的 I/O 电压

• 可混合使用 DDR、PHY Lite、MIPI、LVDS 及 GPIO

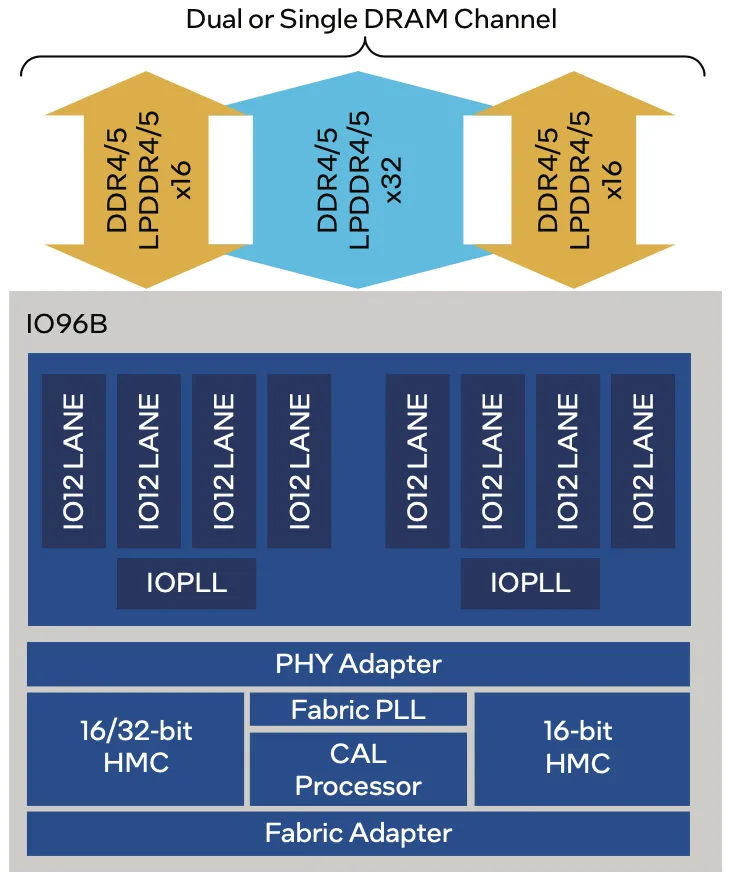

下图展示了单 32 位宽 DDR 接口与双 16 位宽接口的对比情况。对于某些 DRAM 协议,将宽通道拆分为几个窄通道可以提升性能。

Agilex™ 5 支持单通道或双通道DRAM 接口的 I/O Bank

下图展示了在同一 I/O Bank 中混合使用 DDR 与 MIPI D-PHY 通道的示例。其余 I/O 可用作GPIO。每 48 个 I/O 为一组,每组可选择不同的 I/O 电压。例如:MIPI SLVS I/O 可采用 1.2 V 电压,而 LPDDR5 则可选择 1.05 V 电压。

在同一 Bank 中混合使用 DDR、MIPI 和 GPIO

结论

Agilex™ 5 FPGA 和 SoC 可通过以下几方面提供显著优势:

集成硬核内存控制器;

支持包括 LPDDR5 在内的先进 DRAM 标准;

具备更出色的能效表现及更高的每瓦带宽。

文章来源:Altera