在芯片设计验证中,我们常常面临一些外设连接问题:速度不匹配,或者硬件不支持。例如运行在硬件仿真器或FPGA原型平台上的设计,其时钟频率通常只有几十MHz,甚至低至1MHz以下;而真实世界中的外设与协议(如PCIe、高速以太网等)运行在几百兆以上。如此巨大的速度鸿沟,使得将它们直接相连几乎不可行。针对速度不匹配,核心解决方案是引入降速桥(Speed Adaptor)。它是专门用于原型验证 (Prototyping) 或仿真 (Emulation) 环境中的一类硬件适配器,作用是把运行速度和接口特性差异很大的系统连接起来,能够在接近真实系统的条件下进行验证。而针对硬件不支持的场景,则需要借助模型和接口来模拟真实设备的功能与协议。案例一:PCIe 降速桥(PCIe Speed Adaptor)降速桥通常要解决的是速率匹配匹(Speed Adaptation)、协议转换(Protocol Adaptation)、时间解耦(Time Decoupling)、和可控可观测(Debug/Control)等问题。在FPGA原型中,AMD (Xilinx) PCIe PHY的工作频率(Gen1为62.5 MHz,Gen4达500 MHz)已远高于综合后设计的运行频率。另一方面,用户设计若进行分割,性能将进一步降低二十兆以下。这与PCIe PHY的工作频率形成了巨大落差。正因如此,实现可靠的速率匹配成为连接双方的关键。该解决方案的核心是PCIe Switch IP,其多端口能够独立建立链路并工作于不同状态,以此实现协议版本、链路宽度与速率的动态适配。此外,方案还集成PCS、PIPE接口转换等关键IP模块,共同构成一个完整的速率适配解决方案。

图1:PCIe降速桥原理

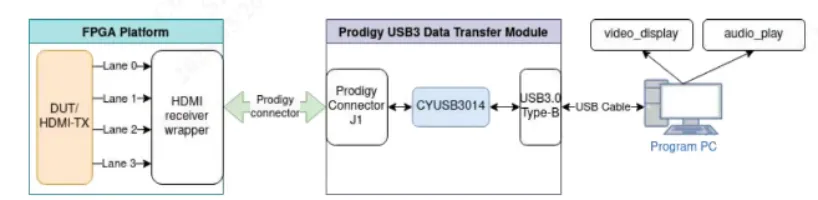

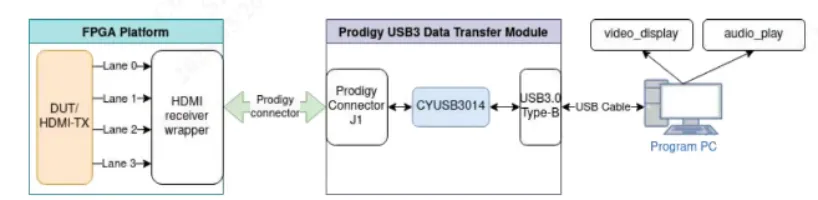

案例二:HDMI 降速桥(HDMI Speed Adaptor)该方案直接将HDMI音视频码流数据传输至主机,通过定制的解码器提取视频和音频数据, 依赖软件模拟显示器,播放解码后的音视频数据。DisplayPort/MIPI DSI/USB Speed Adaptor与之采用相同架构。

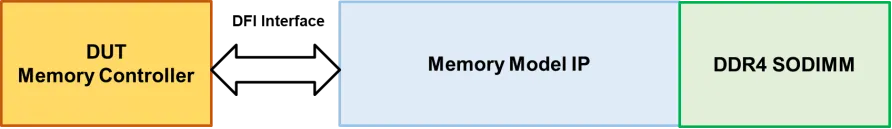

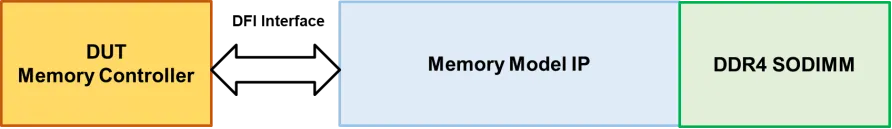

在FPGA原型验证中,为验证DDR5、LPDDR5及HBM2E/3等存储控制器,我们利用Memory Model IP,通过FPGA本身支持的DDR4来模拟这些FPGA无法直接支持的存储器。同时,为了协助系统调试,思尔芯团队为存储器模型增加了一个具备可控性与可观测性的后门,以方便进行高效的读写存储。

凭借在原型验证领域二十多年的技术积累,思尔芯推出了一系列方案以应对复杂的外设连接问题,其代表产品有常用Speed Adaptor、10G-800G速率的高速以太网适配器和存储器模型等,有效帮助客户应对复杂的外设连接问题。公司将持续投入开发,扩展协议支持,并始终致力于运用领先的数字EDA技术,贴近客户,全力助其缩短验证周期,为产品创新与上市提速。

文章来源:思尔芯