Verilog 代码示例

DeBounce_v.v (2.5 KB)

DeBounce_tf.v (1.5 KB)

简介

注:本页信息主要摘自消抖逻辑电路(VHDL)页面;其设计理念同样适用于Verilog和VHDL实现。

在用户界面中使用机械开关是一种普遍做法。然而当这些开关被触发时,触点通常在稳定状态前会多次弹跳或抖动。现有多种硬件或软件方法可处理这种暂时性信号模糊。本文通过简单数字逻辑电路解决该问题(这是FPGA或CPLD连接按钮/开关时的常见需求)。包含DeBounce模块的通用Verilog代码及测试夹具。

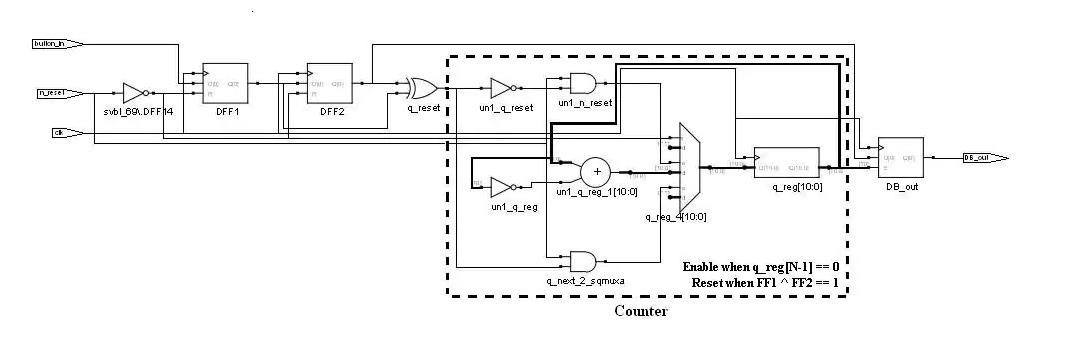

图1展示了所述消抖电路。该电路持续将按钮逻辑电平同步至FF1,再传递至FF2。因此FF1和FF2始终存储按钮最近两个逻辑电平。当这两个值保持相同达到设定时长时,FF3被激活并将稳定值同步输出。

异或门和N位计数器共同实现计时功能。若按钮电平变化,FF1与FF2值将在时钟周期内不同,通过异或门清零N位计数器。若按钮电平无变化(即FF1与FF2逻辑电平相同),异或门释放计数器同步清零端,计数器开始计数。计数器持续递增直至:(1)达到设定时间使能输出寄存器,或(2)因按钮电平未稳定被异或门中断清零。

计数器位数决定验证按钮稳定所需的时长。当计数器递增至进位位有效时,停止计数并激活输出寄存器FF3。电路保持此状态直至FF1输入新按钮值,通过异或门清零计数器。

图 1. 消抖电路

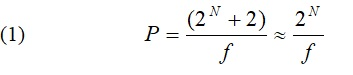

计数器的大小与时钟频率共同决定了验证按钮稳定性的时间周期P 。公式1描述了这一关系。

在典型应用中,时钟周期数较大,因此加载FF2和FF3带来的额外两个时钟周期可安全忽略。

大多数开关在触发后10毫秒内能达到稳定的逻辑电平。假设使用50MHz时钟,需计数0.01*50,000,000 = 500,000个时钟周期以达到10毫秒。19位计数器可满足此需求。如图1所示,利用计数器的进位输出引脚,省去了评估计数器整个输出总线的需求。此方法实现的实际时间为(219+2)/50,000,000=10.49毫秒。

消抖通常不需要高精度,因此通过进位输出引脚确定验证时间引入的较小误差对多数应用已足够。但若需更高时间分辨率,可对计数器部分最高有效位进行逻辑“与”操作,仅需极少额外逻辑资源。

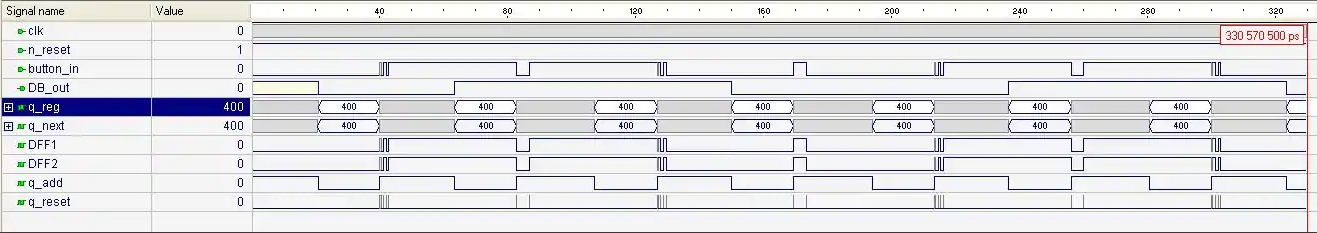

此处提供的示例代码DeBounce_v.v实现了图1所示电路。参数"N"定义计数器大小。图2展示了计数器设为11位(即计数1024次)的仿真结果,该设置便于演示和阅读。相当于2^11/100MHz=20.48微秒延迟。实际应用中此数值不合理,但非常适合演示目的。

图 2.ActiveHDL 仿真结果

该简单逻辑电路解决了可编程逻辑中机械开关的消抖问题。

更多设计支持、产品教程、应用笔记、用户指南等文档可在Lattice官网查阅:https://www.latticesemi.com/zh-CN

文章来源:Digikey