据2025年11月消息,AMD通过官方声明宣布,其Versal RF系列自适应片上系统(SoC)已启动出货。该产品采用单芯片集成设计,将射频采样ADC、DAC与固定功能DSP模块、AI引擎相融合,同时整合射频数据转换器与片上计算能力,可高效完成实时信号处理。其核心优势在于精简嵌入式射频系统的电路板数量、降低功耗,适用场景包括相控阵雷达、测试测量设备,且支持基于LDPC解码的星载通信工作负载。

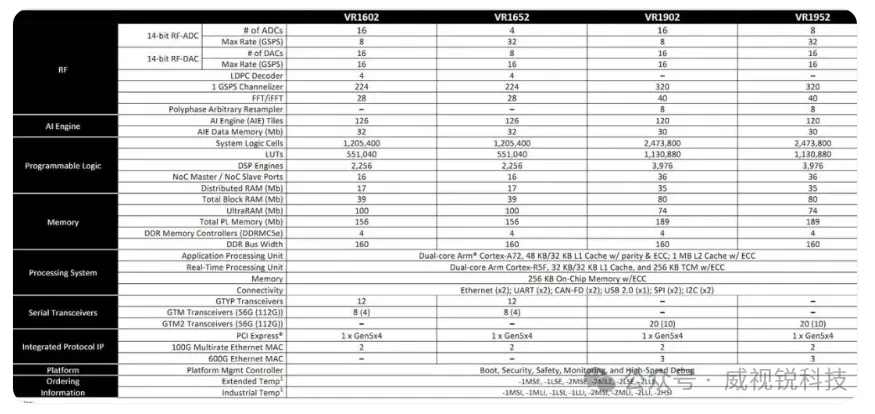

该系列器件具备18GHz输入输出带宽,配置可选最多8个32GSPS或16个8GSPS的14位射频ADC,以及最多16个16GSPS的射频DAC,能实现单芯片宽带频谱捕获与发射。硬件层面集成FFT/iFFT内核、信道化器、重采样器、LDPC解码器、FIR滤波器等,结合AI引擎与DSP58资源提供灵活可编程性。目前VR1602工程样片已交付,VR1652预计2026年一季度上市。

AMD Versal RF 系列产品

(1)概要

AMD Versal RF系列自适应片上系统(SoC)以SWaP优化的单芯片架构为核心,可直接完成Ku波段信号的宽带数字采样,兼具海量数字信号处理能力与边缘端低延迟信号表征特性。

面对现代应用对宽带宽、高采样率及高分辨率的严苛需求,该系列凭借异构计算方案突破传统FPGA架构的DSP资源局限。其整合硬核IP模块、人工智能引擎(AIE)、传统DSP与可编程逻辑,单芯片算力峰值达80TOPS,用户可通过灵活分配各模块处理任务,实现性能与灵活性的精准平衡。

该系列搭载14位带校准功能、32GSPS的射频模数转换器(RF-ADC),是业界首款与自适应逻辑单片集成的最高分辨率RF-ADC。竞品若要达到同等算力,需额外配置FPGA资源,封装面积将增至三倍;而其硬核IP模块执行信号处理的方案,相较软核实现可节省80%动态功耗,成为满足严格SWaP限制且不妥协性能需求的优选方案。

(2)核心优势

宽带信号表征精准高效

搭载最多8个14位(带校准功能)、32GSPS的RF-ADC,集成硬核数字上变频器(DUC)与数字下变频器(DDC)IP核,可实现快速、高分辨率且灵活的宽带频谱表征;具备18GHz瞬时输入带宽,提供更宽广的输入频率通道;同时配置最多16个14位(带校准功能)、16GSPS的RF-DAC,全面满足射频发射需求。

数字信号处理算力充沛

信号处理功能基于硬核IP核实现,支持FFT/iFFT、信道化器、多相任意重采样器及LDPC解码器(含 DVB-S2/S2X 协议);通过人工智能引擎模块、DSP58引擎与硬核IP模块的协同,单芯片算力峰值可达80TOPS;硬核IP模块提供的海量DSP算力,支持单器件部署完整解决方案,无需额外扩展。

尺寸、重量及功耗(SWaP)优化显著

相较于软核IP实现方案,硬核IP模块可将动态功耗降低80%;采用单片集成设计,大幅缩减模数接口的占用面积与功耗;更低的热负荷设计,进一步助力系统尺寸与重量的精简,适配严苛部署环境。

(3)核心应用场景

测试与测量:高速多通道测试仪、宽带频谱分析仪、示波器、6G测试仪

无线通信:准6G系统

AMD 顶级自适应 SoC 重磅亮相内置 RF 采样转换器,DSP 算力达 80 TOPS

Versal RF系列SoC凭借高分辨率多通道RF转换器与低延迟处理技术,可同步捕获并分析宽带频谱。其单片集成的14位(校准后)RF-ADC 拥有32GSPS采样率与18GHz工作带宽,能在宽可观测频谱内快速、精准、灵活地解析信号特征,广泛适用于相控阵雷达、电磁频谱作战、信号情报及卫星通信终端等关键任务领域。

Versal RF系列为高速示波器、宽带频谱分析仪、信号发生器等 T&M应用提供高度集成解决方案,支持Ku频段RF通道及任意重采样、频谱分析等高级T&M信号处理功能。其18GHz直接RF采样与32GSPS采样率的高性能配置,可实现多通道数GHz RF带宽的同步数字化。

Versal RF系列的数字信号处理器(DSP)计算能力可达80TOPS(DSP 核心功能为数字信号处理),通道化模式下,DSP性能较前代AMD Zynq UltraScale+ RFSoC器件提升高达19 倍。

部分DSP功能由专用硬件IP模块承载,包括4 GSPS FFT/iFFT、信道化器、多相任意重采样器与LDPC解码器,较AMD软逻辑实现方案,动态功耗最高可降低80%。

Versal RF系列的开发工具已正式推向市场。该系列的硅片样品及评估套件计划于2025年第四季度正式上市,量产阶段则预计在2027年上半年启动,标志着产品从研发验证向规模化供应迈进。

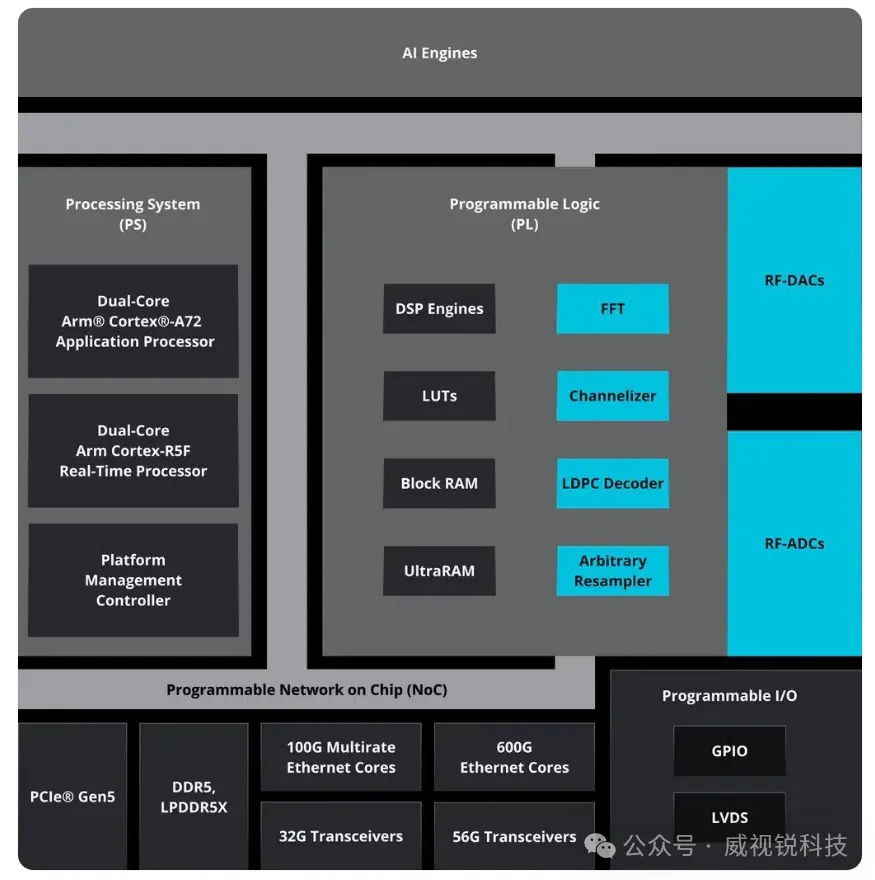

Versal作为AMD(原 Xilinx)推出的自适应计算加速平台系列,聚焦高性能计算、AI加速及嵌入式系统应用,整合了FPGA、AI引擎、多核处理器等异构资源。凭借灵活的硬件架构与高效片上通信机制,该平台可满足多样化计算需求,关键要点如下:

异构计算架构设计

Versal平台采用 “FPGA+ARM” 混合异构架构,通过集成可编程逻辑(PL)、AI引擎、Arm处理器系统(PS)等核心功能模块,构建硬件加速与软件控制深度协同的计算架构,实现高效任务分配与执行。

核心硬件单元详解

AI引擎:专为机器学习算法量身优化的计算阵列,具备高吞吐量矩阵运算能力,可高效支撑深度学习训练与推理任务。

可编程逻辑(PL):延续传统FPGA核心资源特性,支持用户基于业务需求自定义硬件加速电路,适配差异化场景的计算需求。

处理器系统(PS):搭载双核Cortex-A72应用处理器单元(APU)及实时处理器,主要承担系统整体控制、任务调度及通用计算任务,保障系统稳定运行。

高速互连网络(NoC):采用128位宽片上网络设计,支持AXI协议转换功能,可实现跨模块、低延迟的数据传输,提升整体架构的通信效率。

片上网络(NoC)与通信机制

片上网络(NoC)是平台数据传输的核心骨干,通过预定义路由表与QoS策略保障带宽合理分配,核心特性包括:

协议兼容:支持AXI3/AXI4/AXI4-Stream接口自动转换,适配多协议互联需求;

自动配置:启动阶段由PMC控制器通过NPI接口完成初始化,无需用户手动操作;

简化设计:AXI NoC IP助力PL与DDR控制器、PS间的连接设计更高效。

系统管理与启动机制

平台管理控制器(PMC):

承担启动序列管控(含 BootROM 加载 PLM 固件)、电源分配管理、安全状态监测等核心系统服务。内置三类闪存控制单元,支持通过NOR/NAND Flash存储介质或以太网等辅助接口启动系统。

典型应用场景

数据中心加速:针对AI推理、视频转码等算力密集型场景,借助AI引擎与可编程逻辑(PL)的协同工作,实现运算效率的大幅提升。

5G通信领域:依托Multi-Rate Ethernet MAC(MRMAC)及低延迟网络片上系统(NoC)技术,高效完成基站信号处理任务。

工业控制场景:由自适应处理单元(APU)运行Linux操作系统负责整体控制,可编程逻辑(PL)专门承载实时运动控制算法的运算。

开发效率优化

该平台采用软硬件解耦的架构设计(例如 Vitis 工具链支持),开发者可分别在处理系统(PS)端部署应用层软件,在可编程逻辑(PL)端实现定制化硬件加速逻辑,从而显著提升复杂系统的开发效率与灵活性。

文章来源:威视锐科技