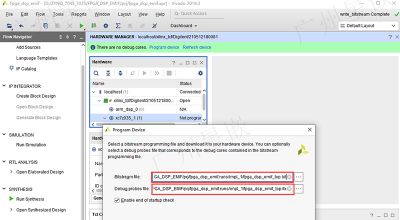

Versal: JTAG TDO

judy 在 周一, 03/13/2023 - 15:50 提交

本文则着重探讨 JTAG TDO 用例

本文则着重探讨 JTAG TDO 用例

在进行 Verilog 设计中,一般会考虑三个基本参数:速度、面积、功耗

本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ与DSP之间EMIF16通信的功能

科技即生产力,最近,OpenAI 发布了 ChatGPT,在各大论坛和许多网站上受到了广泛关注

本文涵盖了有关使用 PetaLinux 命令行来对 Versal™ ACAP 的 PetaLinux BSP 运行 QEMU 的信息

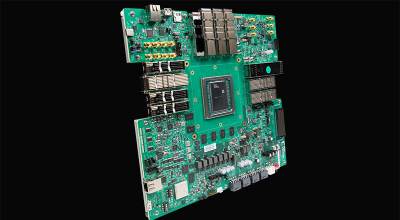

本文详细描述了VPK180评估板的功能

本文提供了仿真进程以及 Vivado® Design Suite 中的仿真选项的概述

在本文中,我们将结合这些层来创建一个完整的推理函数

本文介绍使用Xilinx SDK软件查看当前Zynq SoC启动模式的步骤

FPGA的实现过程可以对综合后生成的网表进行逻辑综合优化、以及布局、布线方面的优化