AMD第二代3D V-Cache的技术细节,首次曝光

judy 在 周一, 03/06/2023 - 09:53 提交

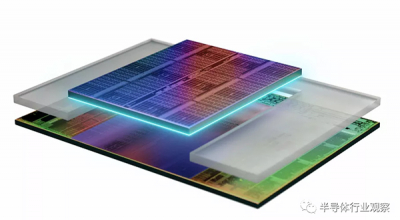

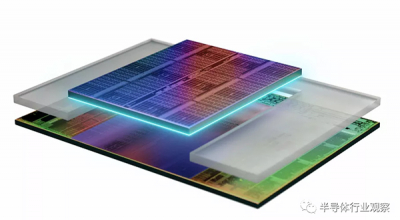

AMD 的第二代 3D V-Cache 技术比第一代技术向前迈出了令人印象深刻的一步

AMD 的第二代 3D V-Cache 技术比第一代技术向前迈出了令人印象深刻的一步

FPGA设计中常见的一个场景就是逻辑需要查存放在外部DDR中的表项,如果查外部DDR中的表项是性能瓶颈点怎么办呢?

DPHY需要完成初始化, 当clock lane和data lane的init_done置高, 以及stopstate拉高

本文主要介绍说明XQ6657Z35-EVM评估板Cameralink回环例程的功能、使用步骤以及各个例程的运行效果

4D毫米波雷达与传统雷达不同,为了解决传统毫米波雷达角分辨率低、点云密度低的问题,当下出现了四种4D毫米波雷达解决方案

此 API 函数为请求的 RF-ADC 设置抽取因子,并根据抽取因子更新 FIFO 写入宽度

随着农业生产模式和视觉技术的发展,农业采摘机器人的应用已逐渐成为了智慧农业的新趋势

本文使用官方BSP,直接创建工程。此步骤根据自己的需求进行建立

本文借鉴网上常见的远程更新QSPI FLASH的相关示例,对表贴式SD卡的应用程序进行了在线更新的操作适配

在本文中,我们将实现其余未实现的层:全连接层、池化层和激活函数 ReLU。