赛灵思@CVPR:学术与实践“双引擎”发展

judy 在 周三, 07/07/2021 - 10:18 提交

本届 CVPR 上,来自北京的赛灵思 AI 研发团队的论文《RankDetNet:深入研究目标检测中的排序约束》成功入选。同时,在 CVPR 期间的自动驾驶研讨会“ Waymo 开放数据集挑战赛”上,赛灵思北京 AI 研发团队又获得“实时 3D 检测”第三名。

本届 CVPR 上,来自北京的赛灵思 AI 研发团队的论文《RankDetNet:深入研究目标检测中的排序约束》成功入选。同时,在 CVPR 期间的自动驾驶研讨会“ Waymo 开放数据集挑战赛”上,赛灵思北京 AI 研发团队又获得“实时 3D 检测”第三名。

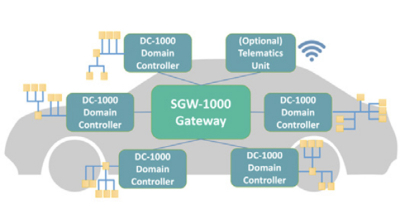

目前,汽车市场对软件定义功能和应用的需求越来越旺盛,行业正迫切需要一种先进的网关,能够提供通用性并为客户提供数据加速和数据分析功能。此外,由于 OEM 车辆和软件定义车辆在需求上存在较大差异,因此需要一种功能更强大且良好平衡的通用型解决方案。

8月3日-12日,赛灵思软件与 AI 专家团特举办四期系列线上公开课,深入探讨如何在调整部署平台架构,满足应用不断增长的挑战与其独特需求的同时,一如既往地使用 TensorFlow 和 Caffe 等高层次框架,采用 C、C++ 和 Python 等熟悉的编程语言进行开发。

了解 Xilinx 和 Cisco 如何利用 Keysight 的 Open RAN Studio 解决方案来验证具有 CPRI 接口的 [仿真] 传统无线电单元的运行和性能,以及 Xilinx 大规模 MIMO O-RU 参考设计,通过采用 Xilinx 技术的 Cisco 基站路由器共享基于以太网的通用 eCPRI 前传网络,最终将在传统 RU 和 O-RAN DU 之间执行前传网关功能。

瑞萨电子的 Xilinx FPGA 参考板是一个扩展电源,旨在为 Xilinx Artix-7、Spartan-7 和 Zynq-7000 系列提供各种 Xilinx 电源。插墙式 AC/DC 适配器或台式直流电源可通过板上的桶式插座给该板供电。

本文将重点介绍 PolarFire FPGA 和 Teledyne e2v DDR4T04G72 之间点对点的连接的例子,以及多个 DDR4器件如何与一片 Xilinx KU060 FPGA 连接。

实现确定性延迟是当今许多系统设计中讨论的主题。过去,人们一直在努力提高数据传输速度和带宽。如今的应用则越来越重视确定性——即要求数据包在精确的、可重复的时间点传送。本文将在设备的层面讨论确定性这一主题,以及如何设计超高速数据转换和信号处理系统以保证确定性延迟。

本文描述将隔离设计流程 (IDF) 和动态函数交换 (DFX) 组合到一个设计中。

在 Vivado 2021.1 中,Control, Interfaces and Processing System (CIPS) IP 架构已重新设计。此次升级支持将来自其它 Versal 系列的器件集成到 CIPS IP 内。

VERSALDEMO1Z 是一个和 Xilinx 联合开发的电源参考板,它为 Xilinx Versal ACAP 平台提供完整的电源轨,ACAP 平台包括自适应引擎、人工智能引擎和标量引擎,以及外部的 DDR 存储器。这款参考板已经开放订购,它既可以作为成熟的整套参考设计,帮助客户抢占设计先机,也可以作为评估平台,快速方便地进行电源测试。