【视频】面向 DFX 的 Abstract Shell

judy 在 周一, 06/28/2021 - 09:41 提交

了解 Abstract Shell 如何大幅缩短 Dynamic Function eXchange 设计多用户环境的编译时间并增强设计安全性。

了解 Abstract Shell 如何大幅缩短 Dynamic Function eXchange 设计多用户环境的编译时间并增强设计安全性。

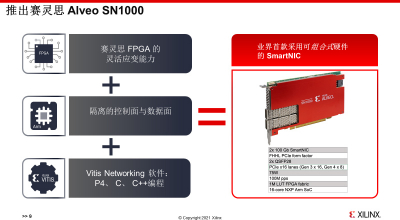

自上世纪80 年代中期首批 PC 机面市后不久,网络接口卡 (NIC) 就已经进入了市场。然而,在过去的几年里,我们看到了 SmartNIC 的兴起。什么是 SmartNIC?按照最基本的定义,SmartNIC 就是可编程NIC。

Xilinx 已发布了 Zynq® UltraScale+™ RFSoC 的 Gen3 版本,该版本将采样速率高达数 Gs 的射频数据转换器和软判决前向纠错(SD-FEC)功能集成到片上系统 (SoC) 架构中。数代产品组合具备了大量不同的直接射频性能器件,能够满足各种频谱需求和应用。

了解如何在 2021.1 中大幅简化 IP 版本控制

从前,嵌入式系统的开发从硬件开始。现在,可以再加入FPGA!面对应用需求越来越复杂的物联网细分市场,以及快速迭代和成本效益的挑战,选择一种现成套件用于无线传感节点原型设计和调试,是一种兼具开发效率和成本效益的解决方案,而全面的软件环境和优化的硬件平台可加快你的开发进度。在这个一连三集的开发板小系列,我们一起来了解更多

(UG332) 即为《Spartan-3 系列配置用户指南》。在此用户指南中,并未涵盖有关从 SPI 闪存启动时,如何使用内部配置访问端口 (ICAP) 来支持在 Spartan-3AN FPGA 内运行多重启动应用的用例。我们将在本篇博文中讲解此用例。

本期视频邀请到赛灵思高级产品应用工程师陈雯,将介绍 Github 上开源的 Vitis 视频加速库的相关内容,并演示在Avleo U50 的板卡上,从Vitis IDE 中调用Vitis™视觉库的加速内核的应用实例解析。

Xilinx推出具有突破性技术的 Vivado ML 以加速设计收敛并提升 QoR,以及先进的 DFX 功能,可实现时间计算的创新形式。

在查看Xilinx KINTEX-7 FPGA存储器资源时,你会发现它的FIFO生成器支持两种读取选项模式——标准读取操作和FWFT读取操作。什么是FWFT?

赛灵思公司今日宣布推出 Vivado® ML 版,这是业内首个基于机器学习( ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本。与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。