开发者分享 | AXI 基础第 7 讲 - 使用 AXI4-Lite 将 Vitis HLS 创建的 IP 连接到 PS

judy 在 周五, 04/23/2021 - 11:18 提交

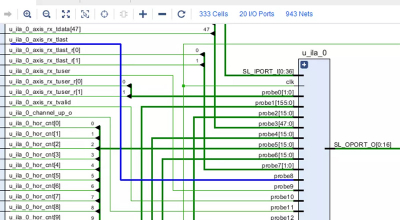

在 AXI 基础第 6 讲 - Vitis HLS 中的 AXI4-Lite 简介中,使用 C 语言在 HLS 中创建包含 AXI4-Lite 接口的 IP。在本篇博文中,我们将学习如何导出 IP 以供在 Vivado Design Suite 中使用、如何将其连接到其它 IP 核与处理器以及如何在板上运行工程。