守护地球,赛灵思在行动

judy 在 周三, 04/21/2021 - 09:53 提交

作为半导体行业的领军企业之一,赛灵思深知解决环境问题对社区、公司和生物多样性的积极影响,因此,赛灵思不拥有或租赁任何高生物多样性保护区的土地。不仅如此,多年来,赛灵思在环保方面所做的努力,已获得多项环保设计奖项,以及业界和政府的认证和肯定。

作为半导体行业的领军企业之一,赛灵思深知解决环境问题对社区、公司和生物多样性的积极影响,因此,赛灵思不拥有或租赁任何高生物多样性保护区的土地。不仅如此,多年来,赛灵思在环保方面所做的努力,已获得多项环保设计奖项,以及业界和政府的认证和肯定。

今天带来第六篇,介绍配置Vitis IDE和项目进出口。

在列车及地面道旁设备上的智能性,可实现快速、安全、可靠、舒适的旅行。控制门、照明、摄像头、空调、制动器、卫生间以及显示器等需要在计算性能、实时性能和可靠性之间达到最佳平衡。 灵活地将人工智能和传感器结合到机舱内部和周围的处理工艺中,为乘客提供更舒适的环境。效率、耐用性和安全性可通过高级牵引控制及优化的电机控制算法在逻辑上进行优化

.mif 和 .coe 是 FPGA 设计中常用的存储文件,用于 ROM、RAM 等存储器数据的加载,常见的还用在 DDS 信号发生器和 FIR 滤波器的设计中。 .txt 文件主要用于 Matlab 和 FPGA 的联合仿真,比如在滤波器的设计中,可以使用 Matlab 先把加噪声的信号写入到 .txt 文件,然后 FPGA 仿真中在 Testbench 中读取该信号源的数据

当你的项目终于做完了,到了发布的关键节点,为了防止自己的心血被别人利用,最好对产品进行bit加密。首先咱们来了解一下加密的优点

ZU+MPSOC器件在汽车电子、工业控制、机器视觉、智能安防、智慧城市等行业中已经有着广泛的应用,三年前在做一个ZCU106开发板的TRD(Target Reference Design)向用户自研板卡移植HDMI设计时,遇到了一些问题,我翻出之前的笔记整理成文,与大家分享。

本文详细介绍了使用Vivado®合成将RTL设计转化为门级网表,以便在Xilinx FPGA中使用SystemVerilog、Verilog和VHDL实现。描述了Vivado综合在项目和非项目模式中的使用,采用多种综合策略和设计约束。

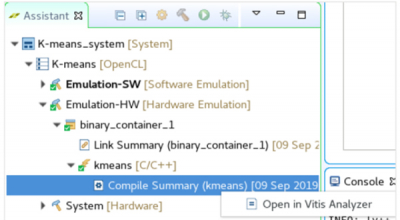

今天带来第五篇,介绍建立系统和Vitis IDE调试流程。

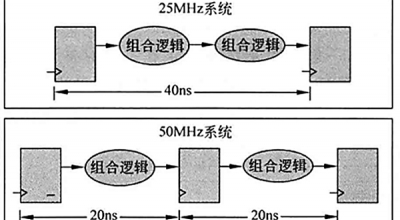

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。

DeepField-SR 是一款功能固定的硬件加速器,该方案采用赛灵思 Alveo 加速卡和 AWS F1云平台,为视频超分辨率增强提供最高计算效率。DeepField-SR 以使用互联网真实视频数据进行训练的专有神经网络为基础,在多帧中融合空间-时间信息,能生成超高分辨率的视频质量。