【视频】数据转换器驱动简介

judy 在 周三, 06/16/2021 - 09:19 提交

本视频演示如何通过 Vitis 统一软件平台访问 Zynq® UltraScale+™ RFSoC 的文档,其中包括 API 和示例文件。

本视频演示如何通过 Vitis 统一软件平台访问 Zynq® UltraScale+™ RFSoC 的文档,其中包括 API 和示例文件。

现在大规模FPGA的bitstream比较大导致板卡从上电到FPGA配置完成的时间远远超过100MS的要求,从而电脑端无法正常识别到PCIE设备。为此Xilinx的PCIE Tandem功能是专为满足PCIe设备在100ms之内枚举起来要求而设计的。

本视频说明了如何消除由 C 设计中的阵列引起的瓶颈。

近日GTIC 2021嵌入式AI创新峰会在北京圆满收官!作为下午场唯一家硬件平台厂商代表,赛灵思公司的软件和解决方案市场部高级经理刘珊珊带来了以《MPSoC平台加速工业视觉应用创新》为题的深入分享。

近几年,边缘计算市场在快速增长,速度超过了数据中心。有统计显示,到2025年,边缘AI芯片的市场机遇是数据中心的3倍,规模将达到650亿美元。这样具有巨大发展潜力的市场,是所有能够参与到其中的芯片厂商特别关注的,无论是CPU、GPU,还是FPGA。作为FPGA行业龙头,赛灵思也已经准备好推出相应的器件

瑞苏盈科(Enclustra)的仙女座XZU90是仙女座(Andromeda)系列的第一款核心板,针对高端应用进行了模块化和优化设计,支持高达6个Samtec ADM6-60高速连接器,提供高达686个用户IO。

就在三年多前,Victor Peng 在 Moshe Gavrielov 退休后接任 Xilinx 首席执行官一职。管理层的转变标志着公司新时代的开始,Peng开始将世界上最大的可编程逻辑公司转变为具有更广泛市场覆盖和增长潜力的公司。 那么,现在,三年后,Peng的 2018 年承诺如何站稳脚跟,Xilinx 下一步将走向何方?

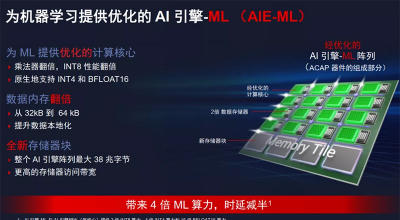

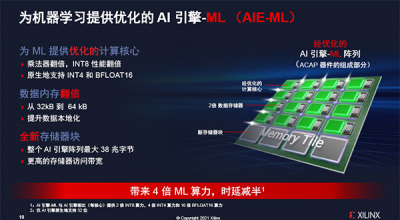

边缘计算芯片领域已经成为了各大巨头的必争之地。6月10日,赛灵思针对边缘市场推出了Versal AI Edge系列产品。该产品是一款自适应SoC,采用了7nm Versal架构,是面向下一代分布式智能系统的全球最具可扩展性且灵活应变的产品组合。

Kria 系列是专门针对边缘部署而精心设计的SOM产品组合,从入门套件到生产SOM,无所不包,可简化系统开发,助力加速产品上市进程。使用面向 Kria K26 SOM 的 KV260 开发平台,用户无需复杂的硬件设计知识也可轻松开发高级视觉应用,本次沙龙我们会介绍两款相关应用

赛灵思今日宣布推出 Versal AI Edge 系列,其旨在支持从边缘到终端的 AI 创新。Versal AI Edge 系列可提供较之 GPU 4 倍的 AI 单位功耗性能,以及较之上一代自适应 SoC 10 倍的计算密度