【ZYNQ Ultrascale+ MPSOC FPGA教程】第十一章 RS232实验

judy 在 周三, 01/06/2021 - 09:49 提交

本章采用AN3485模块的RS232电路实现UART数据传输。

本章采用AN3485模块的RS232电路实现UART数据传输。

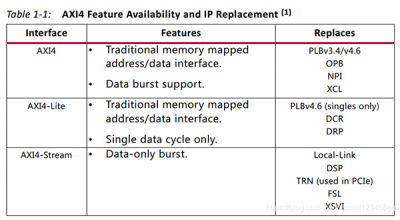

在介绍AXI之前,先简单说一下总线、接口以及协议的含义。总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

串行器/解串器(SerDes)电路多年来一直在帮助芯片间进行告诉数据通信,但新的工艺技术正迫使它以意想不到的方式进行调整和改变。

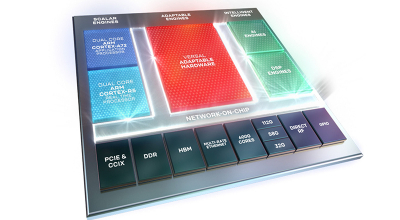

本文档旨在提供 Versal™ ACAP 硬件功能以及创建或移植设计时的块级注意事项的概述,并提供有关设计创建、仿真与调试的方法建议以及有关设计流程、启动和配置的建议。

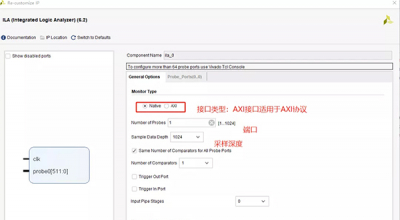

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

本文主要讲解使用PWM控制LED,实现呼吸灯的效果。

2020年是不平凡的一年,纷至沓来的种种变动冲击着全球市场与各行各业。然而,2020年也是危与机并存的一年。变化与挑战之下,赛灵思始终以自适应技术为支撑,为广泛行业领域的合作伙伴提供技术、产品、平台等全方位支持,推动全行业智能化方案落地与转型。

Schedule是和硬件体系结构相关的一些列优化,Halide在其文章中对其做了以下定义,第一条是描述了数据计算顺序对性能的影响,第二条是数据的存储位置对性能影响,最后一条是多线程处理过程中,不同线程数据应该如何进行交互。

XILINX 系列的 FPGA ,如果想要做一个 RAM,有两种方式:

1、使用逻辑资源组成分布式 RAM,即 Distributed RAM

2、使用 XILINX 专用的 Block RAM,即 BRAM

我在xdc文件中匹配目标的时候,在可行的情况下更倾向于使用正则表达式。本文就介绍一下我常使用的正则表达式和一些在Vivado中应用的特殊之处,同时也有个别自己尚未解决的问题。