开箱视频|赛灵思两款全新 Versal 评估套件来了

judy 在 周三, 01/20/2021 - 10:39 提交

日前,赛灵思宣布两款 Versal™ ACAP 评估套件现已上市,分别为 Versal AI Core 系列 VCK190 评估套件和 Versal Prime系列 VMK180 评估套件。VCK190 和 VMK180 评估套件拥有相同的附件集,并且具有相似的板载接口。

日前,赛灵思宣布两款 Versal™ ACAP 评估套件现已上市,分别为 Versal AI Core 系列 VCK190 评估套件和 Versal Prime系列 VMK180 评估套件。VCK190 和 VMK180 评估套件拥有相同的附件集,并且具有相似的板载接口。

前不久,赛灵思联手 Hackster.io 举办首届赛灵思自适应计算挑战赛,号召独立开发者利用 Vitis 统一软件平台和 Vitis AI 在选定的赛灵思硬件平台上开发新应用,以创新方法解决现实问题。在来自全球的 70 多个独创项目中,评委为每个类别甄选出三个冠军项目,分别获得高达 10,000 美元的奖金奖励。

此文基于第十八章内容进行软件开发

本视频将为你介绍如何创建Vitis 嵌入式平台

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加

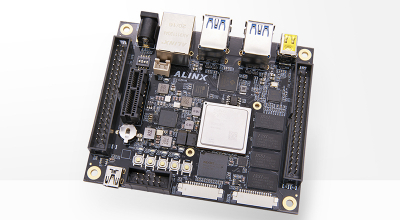

前面的实验都是在PL端进行的,可以看到和普通FPGA开发流程没有任何区别,ZYNQ的主要优势就是FPGA和ARM的合理结合,这对开发人员提出了更高的要求。从本章开始,我们开始使用ARM,也就是我们说的PS,本章我们使用一个简单的串口打印来体验一下Vivado Vitis和PS端的特性。

如何更快更好地解决传统计算模式对图片处理时吞吐速率低、图片处理耗时长、服务器计算资源消耗大等问题呢?FPGA的特性及优势再一次被各类技术关注…

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

本视频介绍了一些关于XRT的要点

为满足合成孔径雷达实时成像、数据回放等高速可靠数据传输需求,解决传统数据传输系统由于接口要求高、体积与功耗大以及网络配置不灵活等原因不适合用于外场试验的问题,基于 ZYNQ 芯片设计一种光纤接口到以太网接口的数据传输系统。主要介绍数据传输流程的实现方法,并提出一种三级乒乓和指令并行的优化策略保证数据正确,提高传输速度