【视频】让自适应计算成为主流

judy 在 周一, 02/01/2021 - 10:16 提交

本视频介绍了赛灵思如何使用FPGA编程更容易被软件开发者和AI科学家使用。

本视频介绍了赛灵思如何使用FPGA编程更容易被软件开发者和AI科学家使用。

打开Petalinux的DeviceTree文件 (比如dtsi文件),经常看到这样的描述,初学者往往困惑,里面这些信息到底说的是什么呢?比如这个 "interrupt-cells = <2>", 里面这个2 或者设定为 1,4,8 到底是什么意思呢?

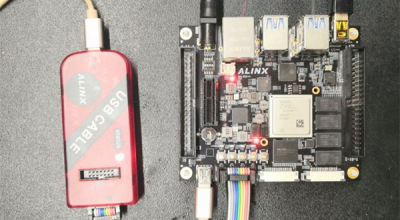

都知道FPGA的启动方式有很多种,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分为主从即Master和Slave(时钟由FPGA的管脚发出,专用的CCLK信号为主,否则为从,有的配置有辅助时钟EMCCLK,它由外部的晶振提供,从FPGA的EMCCLK输入,经过专用的逻辑,再从CCLK管脚输出给想用的器件,),那么问题来了,配置失败怎么办呢??????????????

设备树是 Petalinux kernel 的关键组件,接下来以 2020.1 版本为例,为大家介绍一下在Xilinx Petalinux 工程中的设备树是如何产生,配置以及修改的。

实际性能大比拼:自适应计算平台 vs. CPU/GPU

本章介绍使用FatFs文件系统模块读取SD卡的BMP图片,并通过DP显示。

实现三模(10/100/1000 Mb/s)以太网MAC或10/100 Mb/s以太网MAC。该核心支持使用MII、GMII、SGMII、RGMII和1000BASE-X接口将MAC连接到PHY芯片。它还为SGMII和1000BASE-X模式提供片上PHY。

这次分享一个在Xilinx FPGA实现MIPI DPHY接口的案例(包括CIS协议层)。截止目前为止,Xilinx仅在Ultrascale+及其以上版本的FPGA IO可直接支持MIPI 电平输入,其他的,都需要转换成LVDS来接收。

本视频将介绍Vitis AI 设计流程原理及Vitis AI1.3版的新功能。

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”