Xilinx 联手富士通助力5G在美部署

judy 在 周一, 02/08/2021 - 11:53 提交

赛灵思宣布正为富士通( Fujitsu Limited ) O-RAN 5G 射频单元( O-RU )提供领先的 UltraScale+ 技术。采用赛灵思技术的富士通 O-RU 将部署在美国首个符合 O-RAN 标准的新建 5G 网络中。与此同时,富士通正对赛灵思 RFSoC 技术进行评估,以期为后续更多基站的部署进一步降低成本和功耗。

赛灵思宣布正为富士通( Fujitsu Limited ) O-RAN 5G 射频单元( O-RU )提供领先的 UltraScale+ 技术。采用赛灵思技术的富士通 O-RU 将部署在美国首个符合 O-RAN 标准的新建 5G 网络中。与此同时,富士通正对赛灵思 RFSoC 技术进行评估,以期为后续更多基站的部署进一步降低成本和功耗。

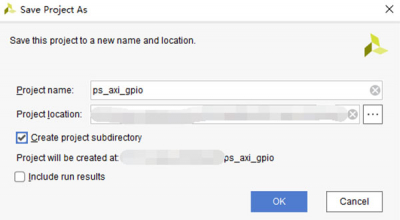

前面讲过如何用的是PS端的EMIO点亮PL端LED灯,但是并没有与PL端产生交互。本章介绍另外一种控制方法,在ZYNQ当中可以使用AXI GPIO,通过AXI总线控制PL端的LED灯。同时也介绍了PL端按键的使用。

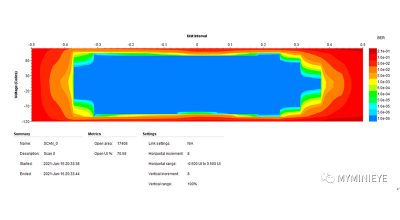

鉴于DNN 在研究和技术方面的巨大投资,很明显,DNN 作为首选解决方案的适用范围,将会继续迅速扩大。然而,在可预见的未来,许多应用将通过传统技术(包括其他形式的机器学习)或通过深度学习和传统算法的组合,来获得最好的解决方案。接下来,我们就一起了解一下,深度学习在机器视觉中的典型应用。

如果想用PS点亮PL的LED灯,该如何做呢?一是可以通过EMIO控制PL端LED灯,二是通过AXI GPIO的IP实现控制。本章介绍如何使用EMIO控制PL端LED灯的亮灭。同时也介绍了,利用EMIO连接PL端按键控制PL端LED灯。

本文档旨在记述用于对赛灵思 FPGA 设计进行编程和调试的 Vivado® 工具。FPGA 编程包括从已实现的设计生成比特流文件和将此文件下载至目标器件。本文档还描述了如何进行设计调试,包括 RTL 仿真和系统内调试。

FreeRTOS在 void vTaskStartScheduler( void )里调用 configSETUP_TICK_INTERRUPT(), 也就是void FreeRTOS_SetupTickInterrupt( void )。void FreeRTOS_SetupTickInterrupt( void )在文件portZynqUltrascale.c里实现

该设计示例演示了如何使用二进制神经网络 (BNN) 加速软件实现的神经网络及可编程逻辑。该演示显示,与纯 CPU 相比,基于 Zynq® UltraScale+™ MPSoC 的电路板可将图像分类速度提高 6000 (Ultra96) 到 8000 倍 (ZCU102)。用户可通过图形用户界面查看指标、图像和分类结果。

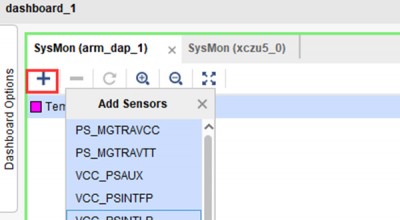

本章介绍system monitors的使用,用于监测芯片的电压、温度值等,也可以通过PL端的ADC引脚作为外部信号的采集。

Zynq UltraScale+ RFSoC 系列为 5G 无线及 RF 类模拟应用带来了颠覆性集成和架构突破性能,其可直接支持整个 5G 的 6GHz 以下频段。这个创新系列现已投入量产。展示了 Zynq UltraScale+ RFSoC 器件不仅可提升灵活性,而且还可简化 5G 系统及软件定义无线电应用。

IBERT(集成误码率测试仪)是xilinx为7系列FPGA GTX收发器设计的,用于评估和监控GTX收发器。IBERT包括在FPGA逻辑中实现的模式生成器和检查器,以及对端口的访问和GTX收发器的动态重新配置端口属性,还包括通信逻辑,以允许设计在运行时通过JTAG进行访问。IBERT工具用于对Xilinx FPGA芯片的高速串行收发器进行板级硬件测试。