【下载】Zynq DPU v3.3 IP 产品指南

judy 在 周二, 02/23/2021 - 09:14 提交

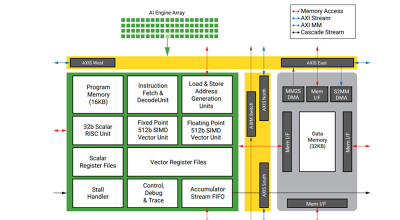

本文描述了用于卷积神经网络的 DPU。

本文描述了用于卷积神经网络的 DPU。

赛灵思公司作为自适应计算的全球领先企业,将携最前沿的观点、技术、核心产品、解决方案与全球最佳实践“盛装亮相” MWC21 上海,与参会嘉宾共同探讨 5G 的创新应用,以及如何通过打造灵活应变的 5G 架构,加速 5G “破茧成蝶”。

源语(Primitives)-Xilinx库中最简单的设计元素。Primitives 基元是设计元素“原子”。Xilinx原语的示例包括简单缓冲区BUF和带有时钟使能和清除功能的D触发器FDCE。

赛灵思Alveo 加速卡,为金融行业定制具有突破性的创新解决方案满足客户和监管机构的需求。本次邀请到赛灵思数据中心及金融行业众多专家,探讨FPGA如何助力金融科技腾飞。

随着智能互联设备的渗透,我们已来到半导体行业发展的拐点。这些智能设备充斥着我们的家庭、汽车、办公室、工厂、城市和云端。而实现无处不在的人工智能( AI )的代价在于,驱动这些设备的半导体器件所要承载的数据处理需求正呈指数级增长

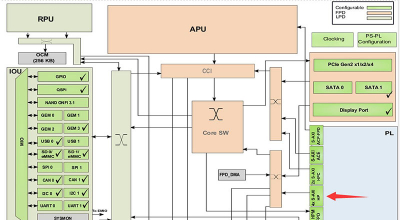

PL和PS的高效交互是zynq soc开发的重中之重,我们常常需要将PL端的大量数据实时送到PS端处理,或者将PS端处理结果实时送到PL端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常麻烦,灵活性也比较差,本节课程讲解如何直接通过AXI总线来读写PS端ddr的数据,这里面涉及到AXI4协议,vivado的FPGA调试等。

由于优异的性能和丰富的功能集,泰克选择了赛灵思 Zynq-7000S SoC。借助 Zynq-7000S 器件,泰克可以更改 TBS1000C 的用户界面,使其与泰克的其他产品匹配。Zynq-7000S SoC 能够将记录长度增加 8 倍,并将波形捕获速率提高 10 倍,在缩短上市时间的同时,实现先进的软件功能和采集功能。

本文重点介绍在Xilinx® Versal™ AI Core器件中使用AI Engine技术的数字下变频链(DDC)设计。展示了一种将DDC功能映射到AI Engine阵列的创新方法,利用Versal ACAP的独特架构来提供高性能和高效率。

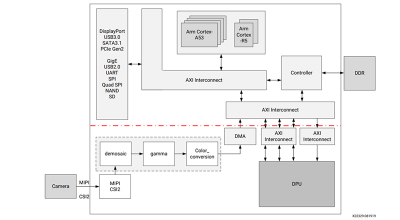

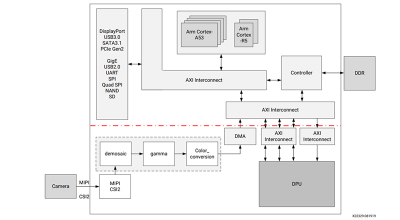

详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的系统与硬件架构。 在详细了解硬件架构之前,先大概了解一下系统架构。 最后将介绍用于启动参考设计的资源。

机器学习 (ML) 技术正在强化交通部门的检测精度和数据分析能力。虽然该技术相对新颖,但它仍在不断演进发展中,且正在成为新的标准。智能交通摄像头广泛应用于收费系统、交通监控、安全保障等。这些系统的打造具有变革性的意义,因为与建设分流路线和更多道路的成本消耗相比,它们对于优化交通流,疏解交通拥挤和堵塞意义深远