汽车电子专场剧透:解构域控制器的个中乾坤

judy 在 周一, 03/01/2021 - 15:39 提交

许多情况下,这些域控制器不仅仅是为一款车而设计,而是为一个支持多款车的平台而设计。主控制器可能具有相当长的生产命周期,而在此期间,软件无疑会更新。因此,它既是域控制器的寿命,也是单个车型的寿命,在某种程度上需要有更新的空间。正因为我们不知道将来会发生什么,灵活性才如此重要。

许多情况下,这些域控制器不仅仅是为一款车而设计,而是为一个支持多款车的平台而设计。主控制器可能具有相当长的生产命周期,而在此期间,软件无疑会更新。因此,它既是域控制器的寿命,也是单个车型的寿命,在某种程度上需要有更新的空间。正因为我们不知道将来会发生什么,灵活性才如此重要。

本白皮书探讨了深度卷积深度学习操作在Xilinx自适应设备上实现。 本白皮书旨在提供针对不同Xilinx器件的多种优化策略,以满足各种任务要求。 在边缘方面,Xilinx实现了轻量级的深度卷积引擎,该引擎支持相应的计算要求。

在软件开发过程中我们经常遇到用 patch 来传递和更新代码的场景。今天赛灵思技术专家以一个端到端的例子来演示在 Petalinux 使用过程中,如何给 u-boot 的源码生成patch 并在 Petalinux 中进行编译。

3月10日与您相约蓉城, 为您带来赛灵思软件与 AI 方向面对面交流活动!本活动全程免费,名额有限。参会资格以微信审核通知为准,迅速报名吧,干货多多,礼品也多多!

在Xilinx FPGA中实现的设计不需要插入全局复位网络。对于绝大多数设计,所有触发器和RAM的上电后的初始化状态比任何的逻辑复位都要全面,不需要为了仿真而插入复位,因为没有任何东西是未定义的

Petalinux可以帮助工程师简化内核模块的创建工作。在petalinux工程目录下,使用命令“petalinux-create -t modules --name --enable”,能创建Linux内核模块,包括c源代码文件、Makefile、Yocto的bb文件。相关文件放在目录“project-spec/meta-user/recipes-modules”,目录结构如下

在 "人工智能引发能源问题,我们该怎么办 (一)"中,我们简要介绍了更高层次的问题,这些问题为优化加速器的需求奠定了基础。作为一个尖锐的问题提醒,现在让我们通过一个非常简单的图像分类算法,来看一看与之相关联的计算成本与功耗。

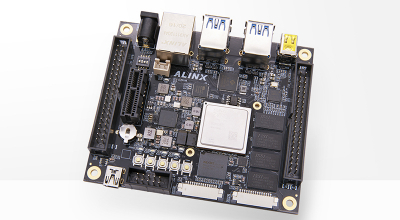

有时CPU需要与PL进行小批量的数据交换,可以通过BRAM模块,也就是Block RAM实现此要求。本章通过Zynq的GP Master接口读写PL端的BRAM,实现与PL的交互。在本实验中加入了自定义的FPGA程序,并利用AXI4总线进行配置,通知其何时读写BRAM。

FPGA 融合了 ASIC 和基于处理器的系统的最大优势,它能够提供硬件定时的速度和稳定性,且无需类似自定制 ASIC 设计的巨额前期费用的大规模投入。但是和所有的数字电路一样,FPGA 电路中也存在毛刺问题。它的出现会影响电路工作的可靠性、稳定性,严重时会导致整个数字系统的误动作和逻辑紊乱。下面就来讨论交流一下FPGA 的竞争冒险与毛刺问题。

2014 年,斯坦福大学教授 Mark Horowitz 发表了一篇题目为“计算的能源问题(以及我们该怎么办)”的论文。这篇具有深远意义的论文,讨论了当前半导体行业所面临的最热门的、与登纳德缩放比例定律 (Dennard Scaling )和摩尔定律 (Moore’s Law) 失效相关的挑战。