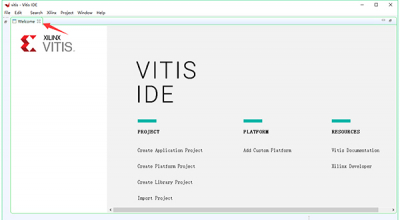

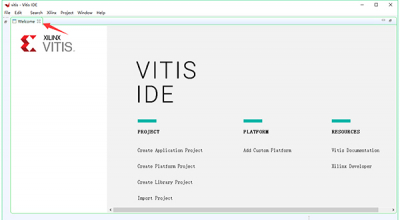

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十七章 Vitis准备工程及注意事项

judy 在 周一, 01/18/2021 - 09:42 提交

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到Vitis_image_download文件夹,覆盖原有的BOOT.bin。也可以把BOOT.bin放到SD卡启动验证功能

所有的工程目录下都有个bootimage文件夹,存放了对应的BOOT.bin文件,可将此文件拷贝到Vitis_image_download文件夹,覆盖原有的BOOT.bin。也可以把BOOT.bin放到SD卡启动验证功能

快速傅立叶变换(FFT)已被广泛应用于各种信号处理算法中,这些算法通常需要可配置FFT大小的高吞吐量。本应用说明展示了在Xilinx® Versal™ AI Core器件中的AI Engine (AIE)阵列上高效的FFT实现。

本视频重点介绍如何在命令行模式下将DPU 作为 HLS 内核与 Vitis 2020.2 和 Vitis AI 1.3 集成。

基于HDMI输出实验,本章介绍7寸液晶屏的显示。LCD屏显示方式从屏幕左上角一点开始,从左向右逐点显示,每显示完一行,再回到屏幕的左边下一行的起始位置,在这期间,需要对行进行消隐,每行结束时,用行同步信号进行同步

在数据的传输过程中,我们经常可以碰见双沿传输数据到FPGA,或者FPGA传输双沿数据给外部芯片,最常见的例子就是DDR芯片。这里说明一下,FPGA内部处理的数据都是单沿数据,那么双沿数据的变换只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。

多输入多输出(MIMO)技术已被许多无线系统采用,以利用信道的空间多样性。本应用说明展示了在Xilinx® Versal™ AI Core器件的AI Engine阵列上高效实现波束成形功能。

视频首先简要介绍 Vitis AI,然后逐步介绍 Vitis AI 1.3 工具的端到端使用。

在本文中,我们将重点放在如何能够在不需要特殊的库或类的情况下修改代码风格以实现C代码实现并行性。Xilinx HLS 编译器的显着特征是能够将任务级别的并行性和流水线与可寻址的存储器 PIPO或 FIFO相结合。

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这个实验更加深入的了解HDMI的显示方式。

配备业界首个自适应计算加速平台(ACAP)的 Xilinx Versal AI Core 系列 VCK190 评估套件和 Versal Prime 系列 VMK180 评估套件现已推出。