宏景智驾携多家合作伙伴共建开放式自动驾驶生态圈

judy 在 周二, 12/22/2020 - 16:03 提交

由宏景智驾与英特尔、赛灵思、江淮汽车、安能物流联合发起的面向量产的开放式自动驾驶生态朋友圈今日正式启动运作,旨在不断积聚科技智慧,拓宽中国自动驾驶领域的创新之路。同日,自动驾驶生态圈联合发布“L3级自动驾驶重卡解决方案”,加速推动自动驾驶技术在干线物流领域的商业化量产落地进程。

由宏景智驾与英特尔、赛灵思、江淮汽车、安能物流联合发起的面向量产的开放式自动驾驶生态朋友圈今日正式启动运作,旨在不断积聚科技智慧,拓宽中国自动驾驶领域的创新之路。同日,自动驾驶生态圈联合发布“L3级自动驾驶重卡解决方案”,加速推动自动驾驶技术在干线物流领域的商业化量产落地进程。

Vitis AI 1.3 将为用户提供更完整的深度学习框架和模型支持,进一步整合了从边缘端到数据中心端的编译流程,首次发布面向数据中心平台的多个 CNN 及 RNN加速引擎,更加开放、高效和易用。

为 VCU129 开发板提供的 BOARDUI.exe 可用于为板载 Si5348 时钟模块编写程序。默认频率为 156.25Mhz,该频率的设置文件在 BOARDUI 的 clockFiles 目录下提供。如何修改时钟频率?

本文主要介绍verilog基础模块,夯实基础,对深入学习FPGA会有很大帮助。

TVM主要的编译过程如下图:Import:将tensorflow,onnx,pytorch等构建的深度学习模型导入,转化成TVM的中间层表示IR。Lower:将高层IR表示转化成低阶TIR表示。Codegen:内存分配和硬件可执行程序生成。

需要使用 Vitis 可扩展平台才能启用 Vitis 加速功能。本视频将引导您完成创建 Vitis 嵌入式平台,并向您展示如何创建自定义平台。

本文主要介绍如何使用Vivado 开发套件创建硬件工程。

NeoPixels是数字控制的红、绿、蓝像素。由于每种颜色都由8位表示,总共24位,因此每个像素可以显示16777216种颜色中的一种。每个NeoPixel实际上是一个WS2812 LED。这些LED包含五个输入端,相对于地(VSS)在3.3V到5.0V(VDD和VCC)的电压范围内工作。

AXU2CGA/B的特点是体积小并扩展了丰富的外设。主芯片采用Xilinx公司的Zynq UltraScale+ MPSoCs CG系列的芯片,型号为XCZU2CG-1SFVC784I。AXU2CGA的PS端挂载了2片DDR4(2GB,32bit)和1片256Mb的QSPI FLASH。

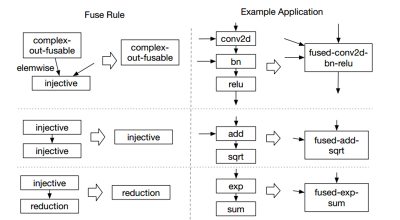

算符融合将多个计算单元揉进一个计算核中进行,减少了中间数据的搬移,节省了计算时间。TVM中将计算算符分成四种:

1 injective。一一映射函数,比如加法,点乘等。

2 reduction。输入到输出具有降维性质的,比如sum。

3 complex-out。这是计算比较复杂的,比如卷积运算等。

4 opaque。无法被融合的算符,比如sort。