【下载】Zynq UltraScale + MPSoC嵌入式设计教程

judy 在 周二, 06/16/2020 - 10:13 提交

本文演示了使用Vivado设计套件和Xilinx软件开发套件构建基于Zynq UltraScale + MPSoC处理器的嵌入式设计。提供有效的嵌入式系统设计的动手教程。

本文演示了使用Vivado设计套件和Xilinx软件开发套件构建基于Zynq UltraScale + MPSoC处理器的嵌入式设计。提供有效的嵌入式系统设计的动手教程。

“以新发展理念为引领,以技术创新为驱动,以信息网络为基础,面向高质量发展需要,提供数字转型、智能升级、融合创新等服务的基础设施体系。”这便是的近来备受关注的新基建。按下快进键的新基建,也在推动着智慧安防、智慧交通和智慧城市等领域的快速发展。

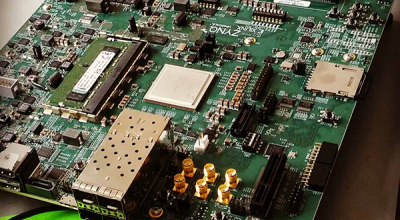

MPSoC EV 系列支持H.265编解码。在规格中,1080p编解码都可以达到8路1080p30,总体相当于1080p240。使用2018.3 VCU TRD 实际测试,性能更好。

在上一篇中着重讲解了DMA的含义和AXI_DMA_IP,本次的重点就是搭建一个AXI_DMA环路工程,并从C语言角度分析其SDK代码

数字频率调制是利用载波的频率传输信息的一种调制方式,FSK是在ASK之后出现的一种调制方式,抗衰落能力较强,在一些衰落信道中应用广泛。

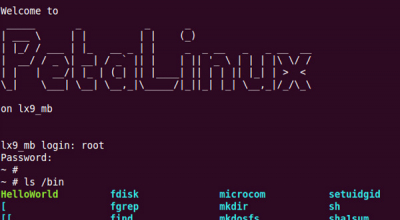

PetaLinux是一个开发和构建环境,可自动执行许多任务,以完成在Zynq®-7000SoC和Xilinx®7系列FPGA上启动嵌入式Linux。本指南包含有关构成PetaLinux工具环境的各种工具的详细信息。

在ZC702单板上,MicroBlaze通过IC/DC端口连接到PS S_AXI_GP0,MicroBlaze读取OCM,得到值DECODE1C。MicroBlaze改为通过DP端口连接到PS S_AXI_GP0,再读取OCM,正常。

改进设计时,如果 QoR 不升反降,那么您势必将面临如下选择。是继续修复?还是重新寻找新的解决方案?您可能忽视了某些问题,或者可能工具在运行给定轮次时性能有所下降。能否快速准确解答这一问题恰恰是判断 FPGA 工程师是否足够出色的标准之一。

Partial Reconfiguration(部分重配置)在现在的FPGA应用中越来越常见,我们这次的教程以Project模式为例来说明部分重配置的操作过程。 这里我们使用的Vivado版本是2017.2,使用的例程是Vivado自带的wavegen工程,并在工程中增加一个计数器模块

所谓创造世界记录,就是以某种方式宣告:“这是我们身为人类的最好成绩。现在让我们一起打破它。”从棒球、吉尼斯世界记录到奥运会,人类在举重、跳高、跑步项目上屡屡打破记录。而在商业领域,能够比竞争对手更快地做出响应并快速进行调整,是一件极具价值的事情。