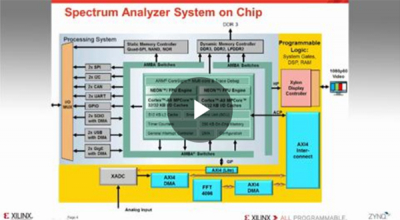

【视频】利用 Zynq-7000 SoC 实现针对 DSP 功能的软件加速

judy 在 周五, 11/16/2018 - 14:21 提交

本演示介绍了 Zynq-7000 SoC 及其利用 NEON 引擎或硬件加速功能实现软件加速的能力。敬请查看 Zynq-7000 SoC 在面向数据采集和加速数字信号处理 (DSP) 的单芯片参考设计中的灵活性优势,其不仅可对软件进行加速,还能充分利用处理器和可编程逻辑之间的低延迟和高性能数据传送功能。

本演示介绍了 Zynq-7000 SoC 及其利用 NEON 引擎或硬件加速功能实现软件加速的能力。敬请查看 Zynq-7000 SoC 在面向数据采集和加速数字信号处理 (DSP) 的单芯片参考设计中的灵活性优势,其不仅可对软件进行加速,还能充分利用处理器和可编程逻辑之间的低延迟和高性能数据传送功能。

作者:骆轶琪 来源:21世纪经济报道

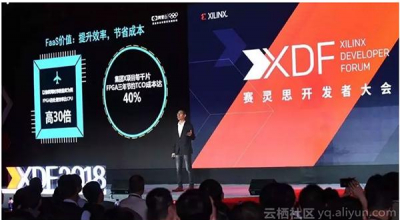

AI时代的来临,也意味着数据爆炸环境下对芯片产业链厂商的进一步考验。不论是背后的算法、架构搭建等,还是具体到对产业的渗透、地区市场的发展,厂商们都将有新的思考。

本文档提供了 Alveo U200 和 U250 数据中心加速器卡的软硬件安装流程。

Alveo U200 和 U250 卡符合 PCI Express Gen3 x16 并采用赛灵思 UltraScale+ 架构。您可以使用这些卡加速计算密集型应用,如数据库加速、机器学习、数据分析和视频处理等。

软件安装流程:

作者:张晓帆

美国伊利诺伊大学、IBM中国研究院等的最新研究,提出一种基于FPGA的DNN推理加速器DNNBuilder,获得电子设计自动化领域学术顶会ICCAD的最佳论文。实验证明,DNNBuilder生成的加速器拥有现时最先进的性能和效率,超越了同类加速器。本文带来论文作者的详细解读。

赛灵思 Alveo U200 和 U250 数据中心加速器卡属于符合 PCI Express Gen3 x16 的加速器卡,设计用于加速密集型计算强度应用,包括机器学习、数据分析和视频处理等。部署 Shell 能让该卡通过 PCI Express 板载存储器完成配置。

Alveo U200和U250产品介绍

2018天猫双11在技术世界,创下不少新记录,其中有一个记录是11日当天阿里全平台共为用户做个性化推荐453亿次,这些推荐的图片长度加起来可以绕地球70圈。

作者:单博,MATLAB

国内的无线通信系统研发过程通常采用的是瀑布式开发的研发方式,项目的开发流程按照从左到右依次分为四个阶段:

如果是的话,您将有机会以特优价格获得 Alveo U200!!!

立即报名参加加速器计划!

加 速 器 计 划

在本教程的带领下,你将在十分钟内学会在PYNQ-Z2板卡上使用传感器和LED开发自己的IoT应用!

初始化板卡

from pynq.overlays.base import BaseOverlay

base = BaseOverlay("base.bit")

赛灵思 Alveo 数据中心加速器卡专为满足现代数据中心变幻莫测的需求而设计。对于常规工作负载,与 CPU 相比性能提升高达 90 倍,这其中包括机器学习推断、视频转码和数据库搜索与分析。