赛灵思FPGA的创新赋能:全球首个无人机5G基站

judy 在 周一, 11/26/2018 - 09:22 提交

在日前上海举行的首届中国国际进口博览会(进博会)上,电子发烧友在赛灵思展台上看到了全球首款无人机5G通信基站,这款创新产品采用了赛灵思的FPGA芯片。

无人机高空基站为全球首款基于5G基站的系留式无人机基站。赛灵思数据中心业务拓展总监朱勇在展会向电子发烧友记者介绍,这款无人机5G基站,采用了赛灵思16纳米的SoC,支持灵活的拆分方式,可以实现100M信号带宽。

在日前上海举行的首届中国国际进口博览会(进博会)上,电子发烧友在赛灵思展台上看到了全球首款无人机5G通信基站,这款创新产品采用了赛灵思的FPGA芯片。

无人机高空基站为全球首款基于5G基站的系留式无人机基站。赛灵思数据中心业务拓展总监朱勇在展会向电子发烧友记者介绍,这款无人机5G基站,采用了赛灵思16纳米的SoC,支持灵活的拆分方式,可以实现100M信号带宽。

对于Vivado Hls来说,输入包括Tesbench,C/C++源代码和Directives,相应的输出为IP Catalog,DSP和SysGen,特别的,一个工程只能有一个顶层函数用于综和,这个顶层函数下面的子函数也是可以被综合的,会生成相应的VHDL和Verilog代码,所以,C综合后的RTL代码结构通常是跟原始C描述的结构是一致的,除非是子函数功能很简单,所需要的逻辑量很小。

时间: 2018年12月20日 | 10:00 - 11:30

从工厂自动化的操作面板到医患监护系统,物联网正改变着所有类型的人机界面(HMI),并因而将网络安全和功能安全,以及混合了云端和本地断的数据扩展至所有这些可视化的信息交互节点。

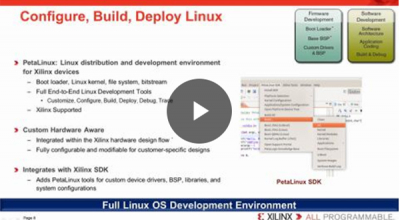

了解可用于 Zynq-7000 可编程 SoC 的不同开发工具。从愿景到部署,Xilinx 开发工具着重端到端开发,包括:系统设计、软件和固件开发、硬件设计、协仿真和调试以及图像生成。

作者:小鱼,Xilinx学术合作

一.概述

在文章《Verilog HDL入门思路梳理》我们说过应该如何去学习Verilog HDL描述。然而第一步,我们需要知道Verilog有哪些语法,它是否可以综合,可以用这个语法来描述什么逻辑功能电路呢?

作者:XCZ ,来源:硬件助手微信公众号

本篇为逻辑电平系列文章中的第一篇,主要介绍逻辑电平相关的一些基本概念。后续将会介绍常见的单端逻辑电平(针对CMOS的闩锁效应进行详细介绍)、差分逻辑电平、单端逻辑电平的互连、差分逻辑电平的互连、一些特殊功能的互连、逻辑互连中的电流倒灌问题、以及逻辑电平的转换等。

由于Vivado下载程序步骤和ISE有较大差异,特此写此文章,希望对大家有所帮助。

Xilinx 机器学习(ML)套件为用户提供了开发和部署机器学习应用进行实时推断所需的工具。它支持许多常见的机器学习框架,如 Caffe、MxNet 和 Tensorflow,以及 Python 和 RESTful API 等。

xDNN v3 将于 2018 年 11 月在 ML Suite 中推出。

解决方案组件

作者:NingHeChuan

作者:四月,机器之能

他们自诩为“搭积木的人”——“FPGA是乐高积木,用最少的积木搭建出整个高楼大厦——这就是我们的能力。”