逻辑电平之差分互连(6-1)

judy 在 周四, 12/06/2018 - 16:56 提交

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

下面详细介绍第一部分:同种逻辑电平之间的互连。

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。由于篇幅比较长,分为两部分:第一部分是同种逻辑电平之间的互连,第二部分是不同种逻辑电平之间的互连。

下面详细介绍第一部分:同种逻辑电平之间的互连。

上世纪 70 年代晚期,以太网之父在施乐帕洛阿尔托研究中心 (PARC) 制作出以太网的雏形 (3Mb/s)。当时他们的研究重点是连接功能,对网络时延或吞吐量关注不多。当时的网络节点是工作站上的工作人员和激光打印机,没人关心数据包在传输过程中是否相互干扰,是否会在抵达目的地前被多次重复发送。在网络中,长短数据包混合传输会给短数据包造成长时延,因为它们需要等待长数据包通过。

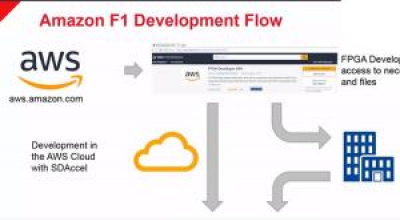

通过本视频教程,您将获得有关 AWS F1实例和 SDAccel 的基本介绍,以及在指导下使用 AWS EC2 F1实例逐步完成您的应用开发。在本视频所介绍的虚拟开发者实验室当中,您将可以连接到 F1 实例,体验 F1实例的加速,并使用 SDAccel 开发和优化 F1 应用。

赛灵思携 Alveo 加速卡亮相一年一度的 IBM OpenPower 中国高峰论坛。

作者:Chetan Khona, 赛灵思工业物联网战略部

上次你看屏幕是什么时候?好吧,这是个诡刁的问题,除非你从事造纸业,或者你名叫摩西 (以色列的先知和首领)并钟情于碑石上篆刻经文,否则你肯定现在就在使用屏幕。毫无疑问,当今时代,屏幕是无所不有、无处不在。

CANopen是一种架构在控制局域网路(Controller Area Network, CAN)上的高层通讯协定,包括通讯子协定及设备子协定常在嵌入式系统中使用,也是工业控制常用到的一种现场总线。CANopen 实现了OSI模型中的网络层以上(包括网络层)的协定。CANopen 标准包括寻址方案、数个小的通讯子协定及由设备子协定所定义的应用层。

此培训视频介绍了如何开发、执行和分析在 AWS F1 上运行的加速应用。观看此视频,了解 SDAccel 执行模型和重要的 OpenCL API,分析和调试功能以及主机代码优化技术。

作者:Mculover666

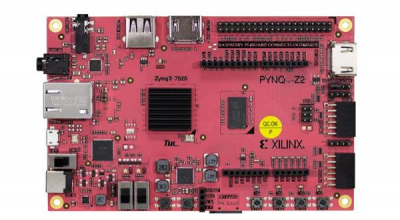

今天刚刚到手一块PYNQ-Z2,确认过眼神,是我想要的板子,话不多说,开干。

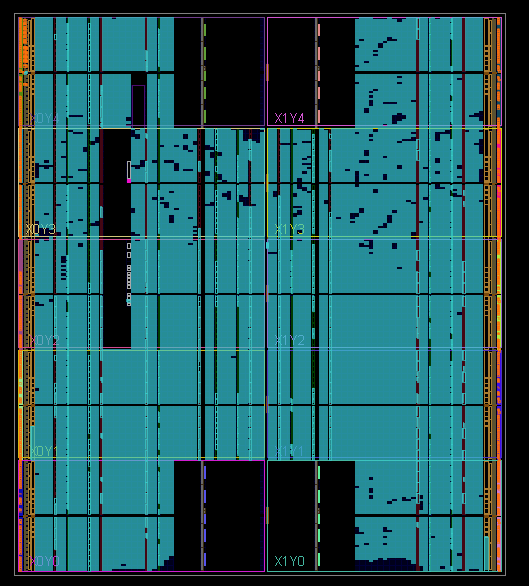

一直以来,觉得自己关于FPGA方面,摸不到“低”——对底层架构认识不清,够不着“高”——没真正独立做过NB的应用,如高速、复杂协议或算法、神经网络加速等高大上的应用,所以能力和认识水平都处于中间水平。这段时间做时序优化,感觉心有余而力不足了,可能要触及手动布局布线了,打开Device布局图才开始有兴趣探究一些底层结构的东西。

看吧,资源已经用了80%的A7 200芯片

可能翻开任何一本有关FPGA的书籍,上来就会介绍FPGA的历史,原理,内部结构什么的,大部分人看着都极其枯燥,常常要么直接略过,要么就看一遍,久了也就忘记了(部分靠翻译文档的书作者该好好反思)。我硬着头皮去弥补之前缺失的一些基础知识,结合Xilinx A7 芯片,总结一下自己的收获。

尊敬的客户:

您好!

在人工智能的浪潮中,依元素科技联合赛灵思、安富利以“聚焦人工智能,助力创新创业”为目标,凭借Xilinx行业领先的技术力量,2018年12月起在全国面向中小AI企业开展一系列的人工智能研讨会,希望帮助中小AI企业成就梦想、同时激发创新机遇。