【tcl学习】vivado write_project_tcl

judy 在 周四, 08/13/2020 - 10:56 提交

每次创建vivado工程时都会生成大量的文件,这样一方面导致占用的磁盘空间很大,另一方面也不利于vivado工程的copy和github上传等操作。这里教大家一个简单又实用的方法,将工程保存成xxx.tcl,只保留ip ,verilog/vhdl和xdc等必要文件即可。

每次创建vivado工程时都会生成大量的文件,这样一方面导致占用的磁盘空间很大,另一方面也不利于vivado工程的copy和github上传等操作。这里教大家一个简单又实用的方法,将工程保存成xxx.tcl,只保留ip ,verilog/vhdl和xdc等必要文件即可。

FPAG在摄像头和激光雷达领域应用广泛。所以FPGA的前景是十分可观的。本文可以帮助大家大概了解FPGA工程师的面试时的热门问题,让大家在面试的时候能提前有所准备,找到理想的工作。

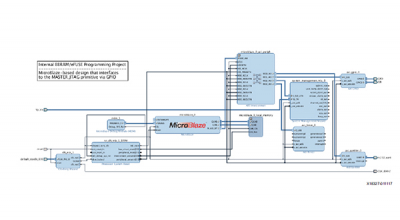

本文提供一个示例,演示如何在UltraScale™和UltraScale +™FPGA中对BBRAM和eFUSE进行内部编程。

在本次网络研讨会上,您将了解 Vitis 环境,以及该环境如何在 Xilinx 平台上实现嵌入式软件和加速应用开发。

Xilinx 自适应计算挑战赛报名持续进行中,借用硬件板卡的流程到8.14日就要结束了~为了让大家更好地学习并掌握Vitis/Vitis A统一软件平台,Xilinx Vitis深入教程首次发布!

对于 AI 推断,在提供与浮点媲美的精度的同时,int8 的性能优于浮点。然而在资源有限的前提下,int8 不能满足性能要求,int4 优化是解决之道。通过 int4 优化,与现有的 int8 解决方案相比,赛灵思在实际硬件上可实现高达 77% 的性能提升。

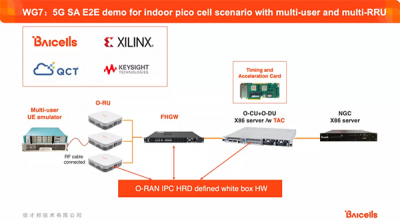

近日,佰才邦(Baicells)联合赛灵思(Xilinx)、QCT、Keysight等合作伙伴,在O-RAN联盟网站上推出并展示了两款基于O-RAN架构的5G SA 端到端( E2E )室内解决方案。此两款基于赛灵思高性能自适应处理器平台方案的面世,将加速通信网络架构开放化和智能化的进程。

在前面的章节中,我们用了很多Tcl的指令,但有些指令并没有把所有的参数多列出来解释,这一节,我们就把约束中的Tcl指令详细讲一下。

本次网络研讨会将深入探讨 Vitis AI 的关键组件,并向您展示如何在 Xilinx 硬件平台上实现灵活应变且高效的 AI 推断。

本章将着重讲述PCIe的MSI和MSI-X中断机制,在FPGA应用中主要通过XDMA中断与上位机进行通信。